## Extended ISDN HDLC FIFO controller with multiple Universal ISDN Ports

(XHFC-2S4U: 2 ST /  $U_p$  interfaces and 2  $U_p$  interfaces) (XHFC-4SU: 4 ST /  $U_p$  interfaces)

Cologne Chip AG Eintrachtstrasse 113 D - 50668 Köln

Germany Tel.: +49 (0) 221 / 91 24-0 Fax: +49 (0) 221 / 91 24-100

http://www.CologneChip.com http://www.CologneChip.de support@CologneChip.com

#### Copyright 1994 - 2012 Cologne Chip AG All Rights Reserved

The information presented can not be considered as assured characteristics. Data can change without notice. Parts of the information presented may be protected by patent or other rights. Cologne Chip products are not designed, intended, or authorized for use in any application intended to support or sustain life, or for any other application in which the failure of the Cologne Chip product could create a situation where personal injury or death may occur.

#### Revision History of XHFC-2S4U/4SU Data Sheet

| Date         | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2012    | Bitmap width of A_SL_CFG.V_CH_SNUM reduced to 4 bit.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|              | Description of bitmaps V_B1_TX_EN, V_B2_TX_EN (both in register A_SU_CTRL0), R_STATUS.V_MISC_IRQSTA and R_IRQ_OVIEW.V_MISC_IRQ slightly changed.                                                                                                                                                                                                                                                                                                                           |

|              | Paragraph concerning HFC-channel processing limitation added to section 3.2.3 on page 80.                                                                                                                                                                                                                                                                                                                                                                                  |

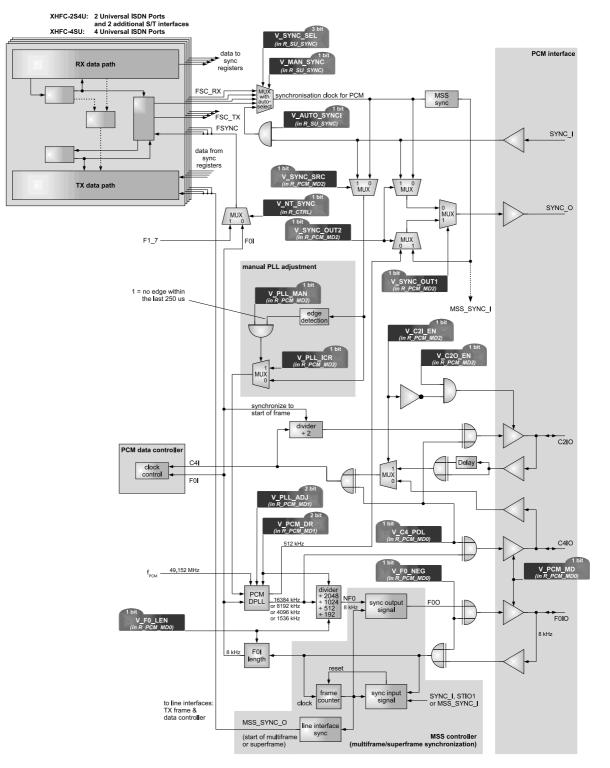

|              | Figure 6.5 (PCM clock synchronization) on page 231 modified concerning C2IO signal path to PCM data controller.                                                                                                                                                                                                                                                                                                                                                            |

|              | Section 9.2.4 (Supply noise requirements for PLL locking) on page 296 added.                                                                                                                                                                                                                                                                                                                                                                                               |

| May 2010     | No changes with regard to contents, only a few typographical corrections have been made.                                                                                                                                                                                                                                                                                                                                                                                   |

| April 2010   | Sections 6.5.6, 6.5.7, 9.1.3.5, 10.3 and 13 added. Figures 9.3 and 10.2 added. Tables 2.3, 10.3, 13.1 and 13.2 added. Register R_SU_LED_CTRL added. Bit V_WD_EN in register R_BERT_WD_MD added.                                                                                                                                                                                                                                                                            |

|              | Reset groups and I/O characteristic of the pin list completely reworked. Section "Reset" also reworked.                                                                                                                                                                                                                                                                                                                                                                    |

|              | Register descriptions improved for e.g. A_B1_RX, A_B2_RX, A_D_RX, A_E_RX, A_FIFO_CTRL, A_SL_CFG, R_CHIP_ID, R_CIRM, R_CLK_CFG, R_FIFO_BL0_IRQR_FIFO_BL3_IRQ, R_IRQ_CTRL, R_IRQ_OVIEW, R_PCM_MD1 and R_RAM_CTRL.                                                                                                                                                                                                                                                            |

|              | Register descriptions clarified and corrected for A_CON_HDLC, A_F1, A_F2, A_SU_CTRL0, R_IRQ_OVIEW, R_PCM_MD1, R_STATUS.                                                                                                                                                                                                                                                                                                                                                    |

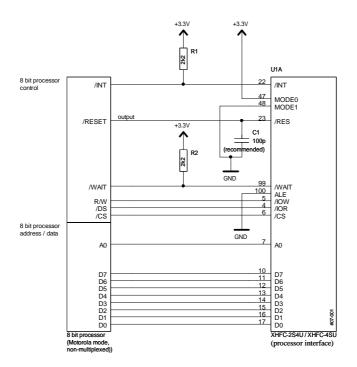

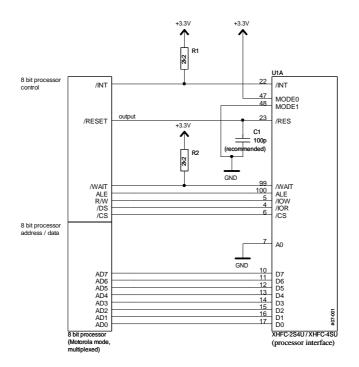

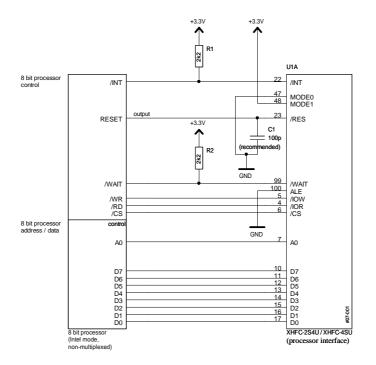

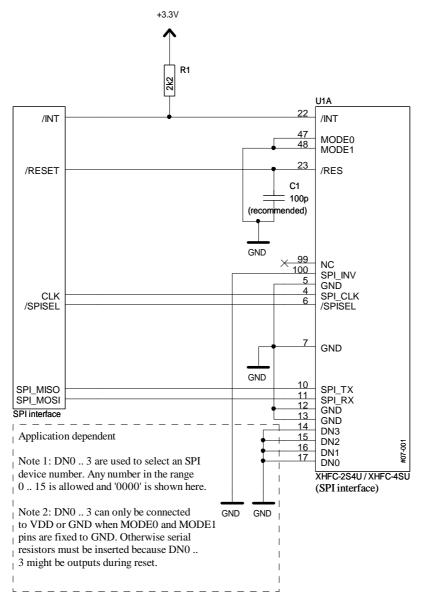

|              | Schematics slightly changed for processor interface (recommended capacitor added), component values of the quarz circuitry improved (see also calculation procedure in section 9.1.3).                                                                                                                                                                                                                                                                                     |

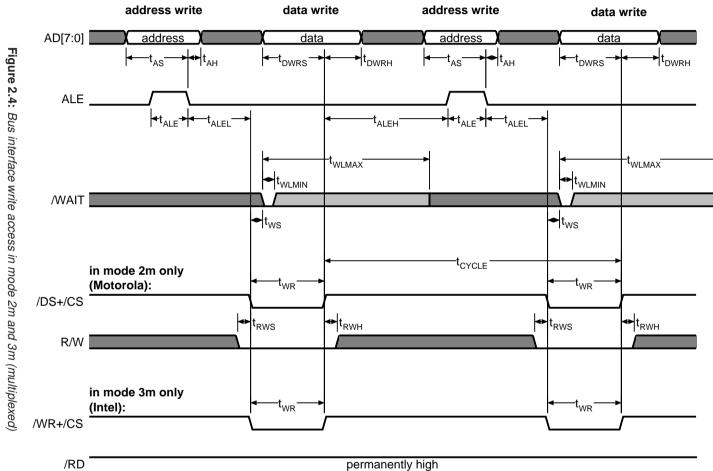

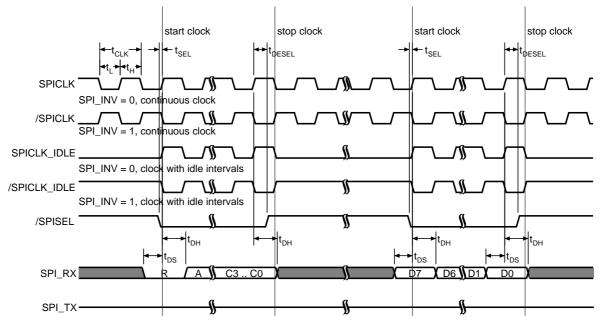

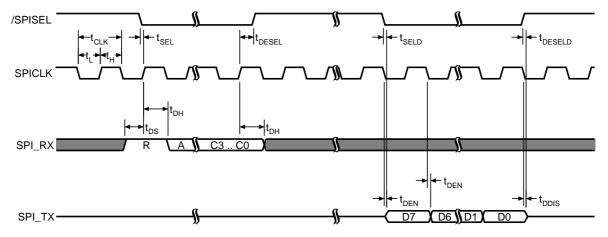

|              | /WAIT signal added to parallel processor interface timing diagrams.<br>Signals /SPICLK, SPICLK_IDLE and /SPICLK_IDLE added to timing diagram 2.20.                                                                                                                                                                                                                                                                                                                         |

|              | Internal signal FSC renamed to FSC_RX (and as a consequence of this FSC_0 and FSC_1 renamed to FSC_TX_0 and FSC_TX_1). Internal signal FSC_TX added to figures 5.1, 5.5, 5.13, 5.15 and 5.16 and to the corresponding sections.                                                                                                                                                                                                                                            |

|              | Note *1 changed in NT state matrices for S/T (Table 5.4) and $U_p$ (Table 5.9) line interfaces.<br>Remarks added for bit scrambler configuration in sections 5.3.4 and 5.3.7.<br>Remark added for monitoring applications in section 5.3.6.<br>Remark concerning internal PCM loop added to section 6.2.<br>Register bit V_FIFO_IRQMSK added to Figure 9.7.<br>Remark concerning unused line interfaces added to section 9.4.4.1.<br>Chapter 11 reworked and supplemented. |

| October 2007 | Minor changes were made in this data sheet revision: Information added to Sections 5.2.6 and 9.4.4.1 concerning state machine behaviour and line interface frequency slip interrupt.                                                                                                                                                                                                                                                                                       |

| July 2007    | C1 and C2 in external S/T receive circuitry moved from L_A /L_B pins to R_A /R_B pins, $t_{AHD}$ added for bus interface write access in mode 2 (Motorola) and mode 3 (Intel), name V_CH_IRQ changed to V_STUP_IRQ in register R_IRQ_OVIEW, name V_FR_IRQSTA changed to V_FIFO_IRQSTA in register R_STATUS, description of many interrupt registers improved.                                                                                                              |

| March 2007   | I/O type and input/output characteristics revised in pin list, pins 12 and 13 changed from NC to GND in SPI operating mode (refer to pin list and SPI connection circuitry), SPI timing diagrams added, section "PCM clock synchronization" restructured and supplemented, application hints for expanding an existing system with ISDN ports added.                                                                                                                       |

# Contents

| Al | oout t | his data | a sheet and Cologne Chip technical support                         | 27 |

|----|--------|----------|--------------------------------------------------------------------|----|

| 1  | Gen    | eral des | scription                                                          | 31 |

|    | 1.1    | System   | n overview                                                         | 32 |

|    | 1.2    | •        | es                                                                 | 33 |

|    | 1.3    | Pin de   | scription                                                          | 34 |

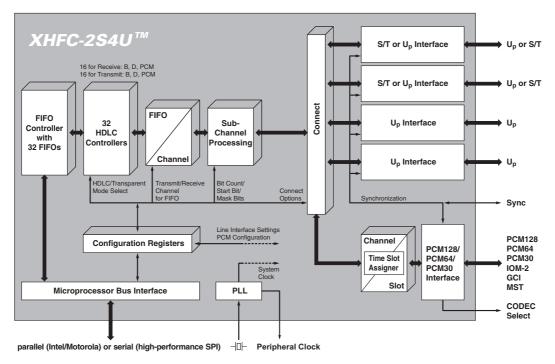

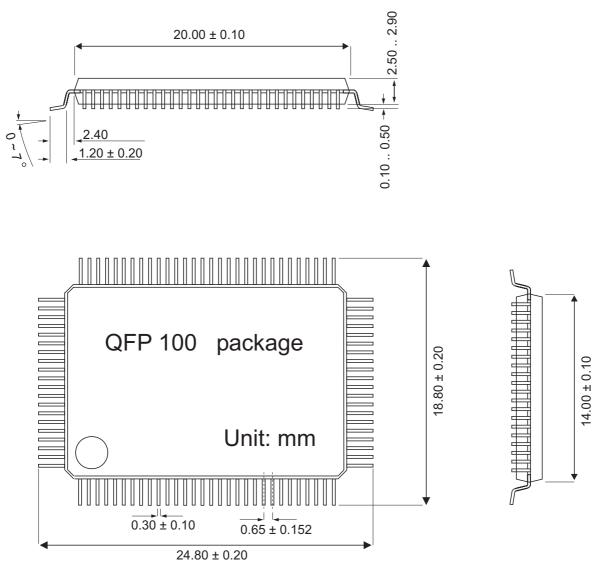

|    |        | 1.3.1    | Pinout diagram                                                     | 34 |

|    |        | 1.3.2    | Pin list                                                           | 36 |

| 2  | Mic    | roproce  | essor bus interface                                                | 43 |

|    | 2.1    | Mode     | selection                                                          | 44 |

|    | 2.2    | Paralle  | el processor interface                                             | 45 |

|    |        | 2.2.1    | Overview                                                           | 45 |

|    |        | 2.2.2    | Interface signals                                                  | 45 |

|    |        | 2.2.3    | Register access                                                    | 46 |

|    |        |          | 2.2.3.1 Non-multiplexed / multiplexed access                       | 46 |

|    |        |          | 2.2.3.2 Read* access                                               | 47 |

|    |        |          | 2.2.3.3 Register address read-back capability                      | 47 |

|    |        |          | 2.2.3.4 Problems with interrupts between address and data accesses | 47 |

|    |        | 2.2.4    | Signal and timing characteristics                                  | 47 |

|    |        |          | 2.2.4.1 Bus interface in mode 2 and mode 3 (non-multiplexed)       | 47 |

|    |        |          | 2.2.4.2 Bus interface in mode 2m and mode 3m (multiplexed)         | 53 |

|    |        | 2.2.5    | Microprocessor connection circuitries                              | 57 |

|    | 2.3    | Serial   | processor interface (SPI)                                          | 59 |

|    |        | 2.3.1    | SPI control byte                                                   | 59 |

|    |        | 2.3.2    | SPI transactions                                                   | 60 |

|    |        | 2.3.3    | Transaction duration                                               | 61 |

|    |        | 2.3.4    | Register write access                                              | 63 |

|    |        | 2.3.5    | Register read access                                               | 65 |

|    |        | 2.3.6    | Register access duration                                           | 66 |

|   |     | 2.3.7   | Register address read-back capability                 |

|---|-----|---------|-------------------------------------------------------|

|   |     | 2.3.8   | Problems with interrupts during transaction sequences |

|   |     | 2.3.9   | SPI timing diagrams                                   |

|   |     | 2.3.10  | SPI connection circuitry                              |

|   | 2.4 | Auto-E  | EPROM mode         71                                 |

|   | 2.5 | Registe | er description                                        |

|   |     | 2.5.1   | Write only registers                                  |

|   |     | 2.5.2   | Read only registers                                   |

|   |     | 2.5.3   | Read / write register                                 |

| 3 | XHF | FC-2S4U | J / XHFC-4SU data flow 77                             |

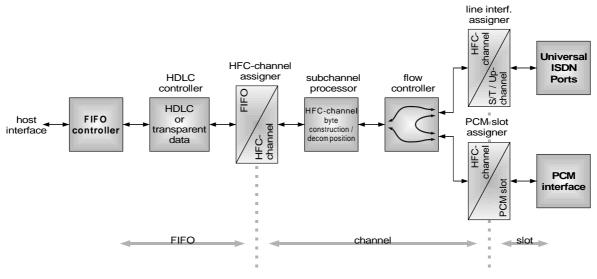

|   | 3.1 | Data fl | ow concept                                            |

|   |     | 3.1.1   | Overview                                              |

|   |     | 3.1.2   | Term definitions                                      |

|   | 3.2 | Flow c  | ontroller                                             |

|   |     | 3.2.1   | Overview                                              |

|   |     | 3.2.2   | Switching buffers                                     |

|   |     | 3.2.3   | Timed sequence                                        |

|   |     | 3.2.4   | Transmit operation (FIFO in transmit data direction)  |

|   |     | 3.2.5   | Receive operation (FIFO in receive data direction)    |

|   |     | 3.2.6   | Connection summary                                    |

|   | 3.3 | Assign  | ers                                                   |

|   |     | 3.3.1   | HFC-channel assigner                                  |

|   |     | 3.3.2   | PCM slot assigner                                     |

|   |     | 3.3.3   | Line interface assigner                               |

|   |     | 3.3.4   | Assigner summary                                      |

|   | 3.4 | Data fl | ow modes                                              |

|   |     | 3.4.1   | Simple Mode (SM)                                      |

|   |     |         | 3.4.1.1 Mode description                              |

|   |     |         | 3.4.1.2 Subchannel processing                         |

|   |     |         | 3.4.1.3 Example for SM                                |

|   |     | 3.4.2   | Channel Select Mode (CSM)                             |

|   |     |         | 3.4.2.1 Mode description                              |

|   |     |         | 3.4.2.2 HFC-channel assigner                          |

|   |     |         | 3.4.2.3 Subchannel Processing                         |

|   |     |         | 3.4.2.4 Example for CSM                               |

|   |     | 3.4.3   | FIFO Sequence Mode (FSM)                              |

|   |     |         | 3.4.3.1 Mode description                              |

|   |            |                | 3.4.3.2     | FIFO sequence                                                            | 101 |

|---|------------|----------------|-------------|--------------------------------------------------------------------------|-----|

|   |            |                | 3.4.3.3     | FSM programming                                                          | 103 |

|   |            |                | 3.4.3.4     | Example for FSM                                                          | 104 |

|   | 3.5        | Subcha         | nnel Proce  | essing                                                                   | 110 |

|   |            | 3.5.1          | Overview    | ·                                                                        | 110 |

|   |            | 3.5.2          | Subchann    | el registers                                                             | 111 |

|   |            | 3.5.3          | Details of  | f the FIFO oriented part of the subchannel processor (part A) $\ldots$ . | 111 |

|   |            |                | 3.5.3.1     | FIFO transmit operation in transparent mode                              | 111 |

|   |            |                | 3.5.3.2     | FIFO transmit operation in HDLC mode                                     | 113 |

|   |            |                | 3.5.3.3     | FIFO receive operation in transparent mode                               | 113 |

|   |            |                | 3.5.3.4     | FIFO receive operation in HDLC mode                                      | 113 |

|   |            | 3.5.4          | Details of  | f the HFC-channel oriented part of the subchannel processor (part B)     | 113 |

|   |            |                | 3.5.4.1     | FIFO transmit operation in SM                                            | 113 |

|   |            |                | 3.5.4.2     | FIFO transmit operation in CSM and FSM                                   | 114 |

|   |            |                | 3.5.4.3     | FIFO receive operation in SM                                             | 114 |

|   |            |                | 3.5.4.4     | FIFO receive operation in CSM and FSM                                    | 114 |

|   |            | 3.5.5          | Subchann    | el example for SM                                                        | 115 |

|   |            | 3.5.6          | Subchann    | el example for CSM                                                       | 120 |

| 4 | FIE        | ) h an dli     |             |                                                                          | 107 |

| 4 |            |                | 0           | DLC controller                                                           | 127 |

|   | 4.1<br>4.2 |                |             |                                                                          |     |

|   | 4.2<br>4.3 |                |             |                                                                          | 128 |

|   | 4.5<br>4.4 |                | -           |                                                                          |     |

|   | 4.4        | 4.4.1          | _           | ansmit FIFOs                                                             |     |

|   |            |                |             |                                                                          | 130 |

|   |            |                |             | c D-channel frame repetition (for S/T in TE mode only)                   |     |

|   |            | 4.4.3<br>4.4.4 |             |                                                                          | 132 |

|   | 15         |                |             | ent mode of XHFC-2S4U / XHFC-4SU                                         | 133 |

|   | 4.5        | 4.5.1          | _           |                                                                          | 135 |

|   |            |                |             | y registers                                                              | 135 |

|   |            | 4.5.2          | -           | y registers                                                              | 140 |

|   |            | 4.5.3          | Kead / wr   | ite registers                                                            | 147 |

| 5 | Univ       | ersal IS       | DN Port     |                                                                          | 157 |

|   | 5.1        | Genera         | l overview  | of the S/T and $U_p$ interfaces                                          | 158 |

|   |            | 5.1.1          | Array reg   | isters and multiregisters                                                | 158 |

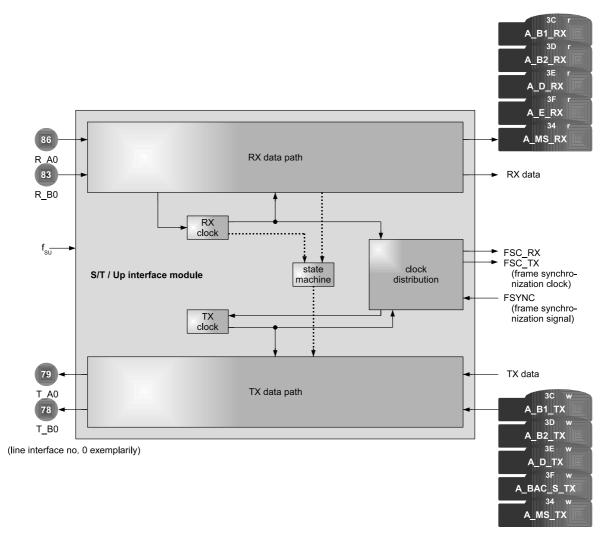

|   |            | 5.1.2          | Block dia   | gram of the Universal ISDN Port module                                   | 158 |

|   | 5.2        | S/T inte       | erface desc | cription                                                                 | 160 |

|   |            | 5.2.1          | Overview    | ·                                                                        | 160 |

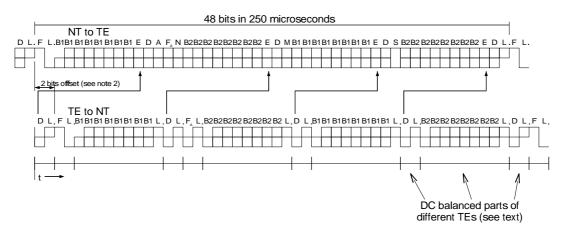

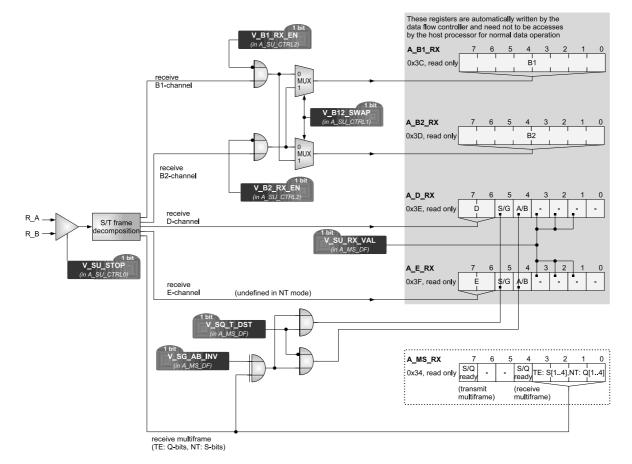

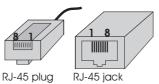

|     | 5.2.2               | Frame Structure                                                                                                        | 160         |

|-----|---------------------|------------------------------------------------------------------------------------------------------------------------|-------------|

|     | 5.2.3               | Multiframe structure                                                                                                   | 161         |

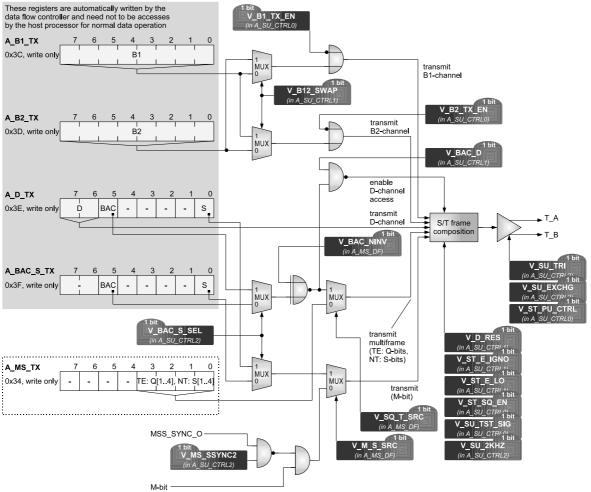

|     | 5.2.4               | Data transmission                                                                                                      | 161         |

|     | 5.2.5               | INFO signals                                                                                                           | 163         |

|     | 5.2.6               | State machine                                                                                                          | 165         |

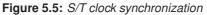

|     | 5.2.7               | Clock synchronization                                                                                                  | 168         |

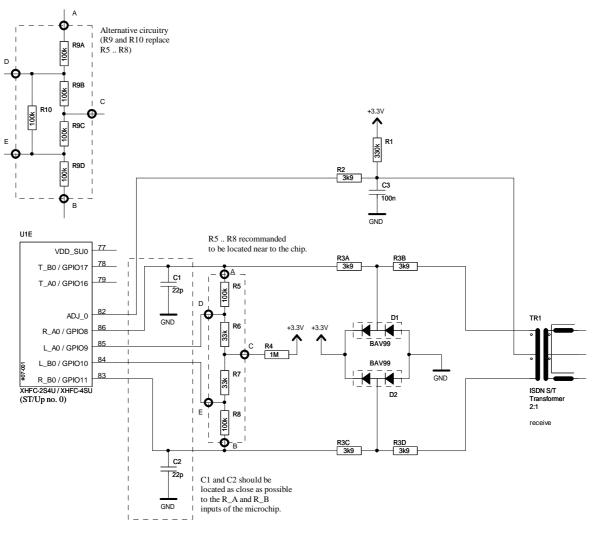

|     | 5.2.8               | External circuitries                                                                                                   | 170         |

|     |                     | 5.2.8.1 External receive circuitry                                                                                     | 170         |

|     |                     | 5.2.8.2 External transmit circuitry                                                                                    | 171         |

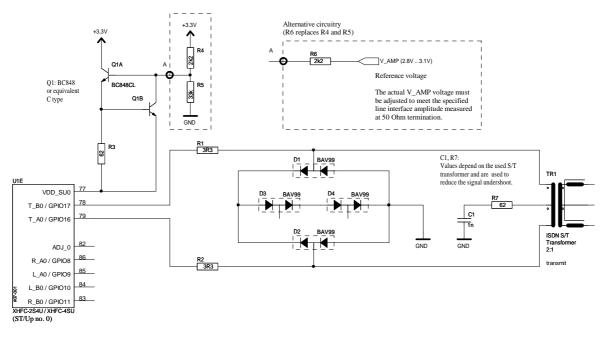

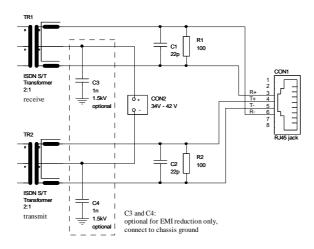

|     |                     | 5.2.8.3 Transformer and ISDN jack connection                                                                           | 172         |

|     | 5.2.9               | S/T transformers                                                                                                       | 173         |

| 5.3 | U <sub>p</sub> inte | erface description                                                                                                     | 177         |

|     | 5.3.1               | Overview                                                                                                               | 177         |

|     | 5.3.2               | Frame Structure                                                                                                        | 177         |

|     | 5.3.3               | Superframe structure                                                                                                   | 177         |

|     | 5.3.4               | Data transmission                                                                                                      | 178         |

|     | 5.3.5               | INFO signals                                                                                                           | 179         |

|     | 5.3.6               | State machine                                                                                                          | 181         |

|     | 5.3.7               | Clock synchronization                                                                                                  | 184         |

|     | 5.3.8               | External circuitry                                                                                                     | 186         |

|     | 5.3.9               | $U_p$ transformers                                                                                                     | 187         |

| 5.4 | Comm                | non features of the S/T and $U_p$ interfaces                                                                           | 188         |

|     | 5.4.1               | Direct data access for test purposes                                                                                   | 188         |

|     | 5.4.2               | Clock synchr. with several TEs connected to different central office switches                                          | 189         |

|     | 5.4.3               | Combined S/T and $U_p$ circuitry $\ldots \ldots \ldots$ | 194         |

| 5.5 | Regist              | er description                                                                                                         | 195         |

|     | 5.5.1               | Write only registers                                                                                                   | 195         |

|     | 5.5.2               | Read only registers                                                                                                    | 211         |

| DCN | A interf            |                                                                                                                        | 221         |

| 6.1 |                     |                                                                                                                        | 221         |

| 6.2 |                     |                                                                                                                        | 222         |

| 6.3 |                     |                                                                                                                        | 225<br>225  |

| 6.4 |                     |                                                                                                                        | 225<br>225  |

| 0.4 | РСМ (<br>6.4.1      | 5                                                                                                                      | 225<br>225  |

|     | 6.4.1<br>6.4.2      |                                                                                                                        | 225<br>225  |

|     | 6.4.2<br>6.4.3      |                                                                                                                        | 225<br>225  |

| 6.5 |                     |                                                                                                                        | 223<br>230  |

| 0.3 | г UNI (             | clock synchronization                                                                                                  | <i>2</i> 30 |

6

|   |     | 6.5.1   | Overview                                                              | 0 |

|---|-----|---------|-----------------------------------------------------------------------|---|

|   |     | 6.5.2   | Manual or automatic synchronization source selection                  | 0 |

|   |     | 6.5.3   | PLL programming for F0IO generation                                   | 0 |

|   |     | 6.5.4   | Manual PLL adjustment                                                 | 0 |

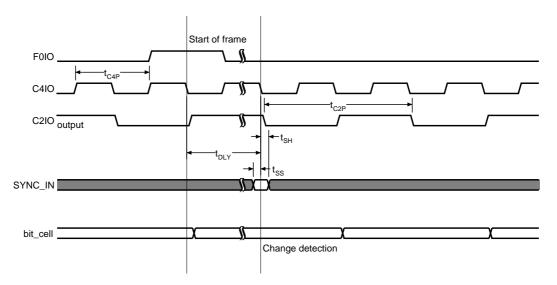

|   |     | 6.5.5   | C2IO signal                                                           | 2 |

|   |     | 6.5.6   | SYNC_O and FSC_RX synchronization signals                             | 2 |

|   |     | 6.5.7   | Synchronous 512 kHz output signal                                     | 2 |

|   |     | 6.5.8   | Application examples for XHFC-2S4U/4SU synchronization schemes 23     | 3 |

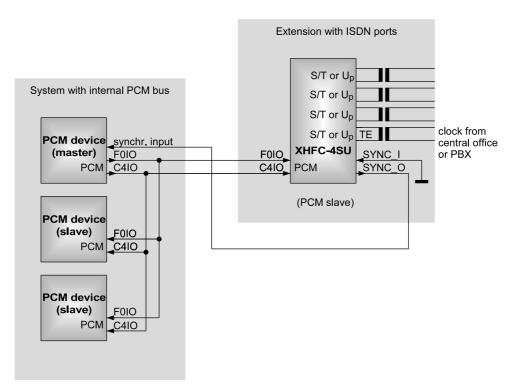

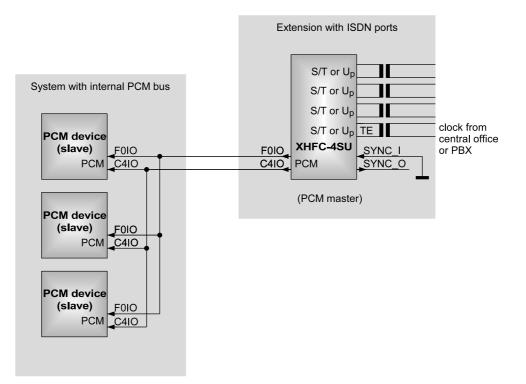

|   |     |         | 6.5.8.1 System with internal PCM bus expanded by ISDN interfaces 23   | 3 |

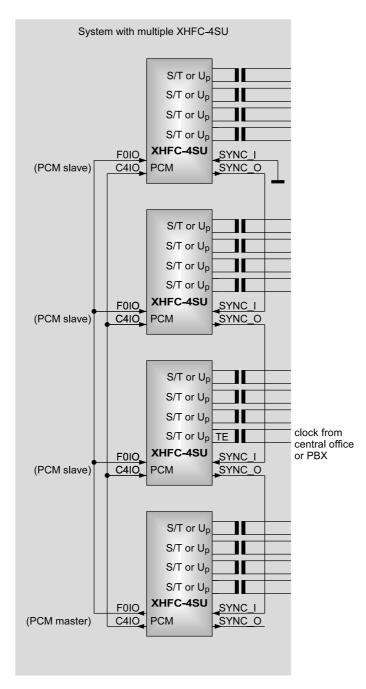

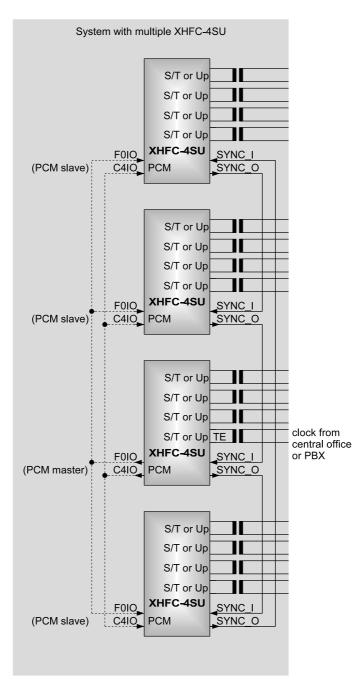

|   |     |         | 6.5.8.2 Application with multiple XHFC-2S4U/4SU                       | 4 |

|   | 6.6 | Multif  | rame / superframe synchronization to the PCM interface                | 7 |

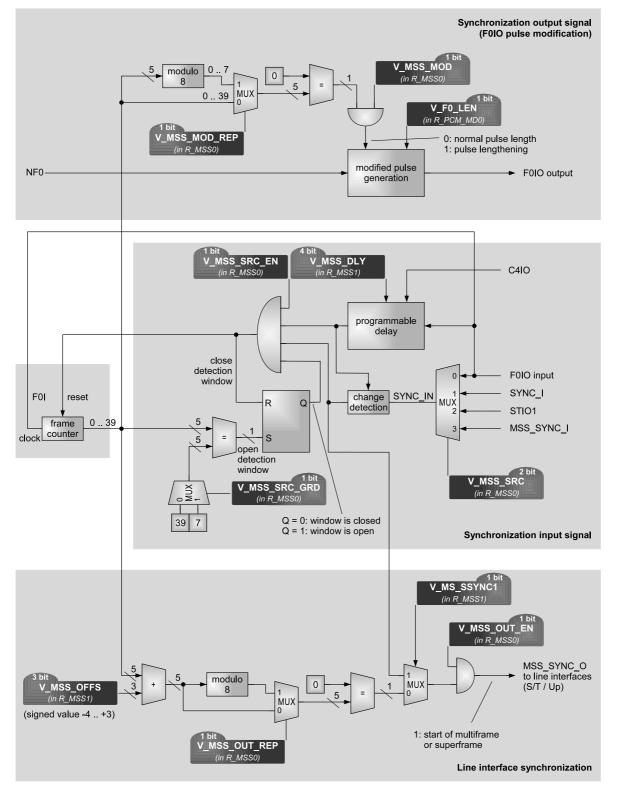

|   |     | 6.6.1   | Overview                                                              | 7 |

|   |     | 6.6.2   | Frame counter                                                         | 7 |

|   |     | 6.6.3   | Synchronization input signal                                          | 7 |

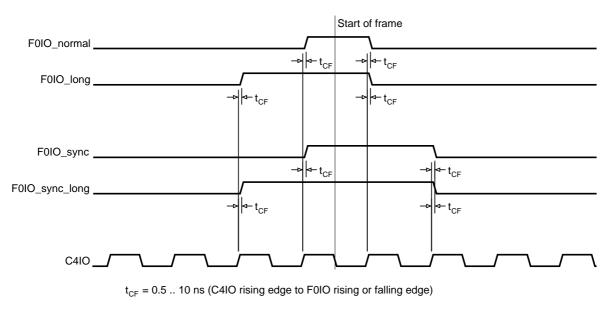

|   |     | 6.6.4   | Synchronization output signal (FOIO pulse modification)               | 0 |

|   |     | 6.6.5   | Line interface synchronization                                        | 1 |

|   | 6.7 | Extern  | al CODECs                                                             | 2 |

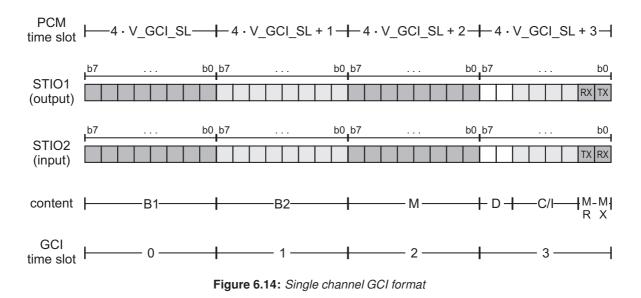

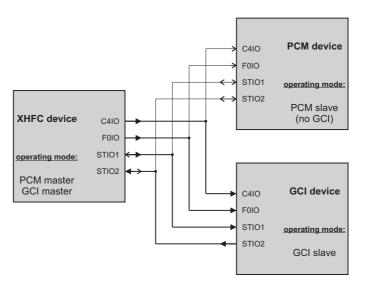

|   | 6.8 | GCI / I | OM-2 mode                                                             | 4 |

|   |     | 6.8.1   | Overview                                                              | 4 |

|   |     | 6.8.2   | GCI frame structure                                                   | 4 |

|   |     | 6.8.3   | GCI register programming                                              | 5 |

|   |     |         | 6.8.3.1 Enable CGI functionality                                      | 5 |

|   |     |         | 6.8.3.2 Monitor channel                                               | 6 |

|   |     |         | 6.8.3.3 Command / indication bits (C/I-channel)                       | 6 |

|   |     |         | 6.8.3.4 Examples for GCI frame embedding in the PCM data structure 24 | 6 |

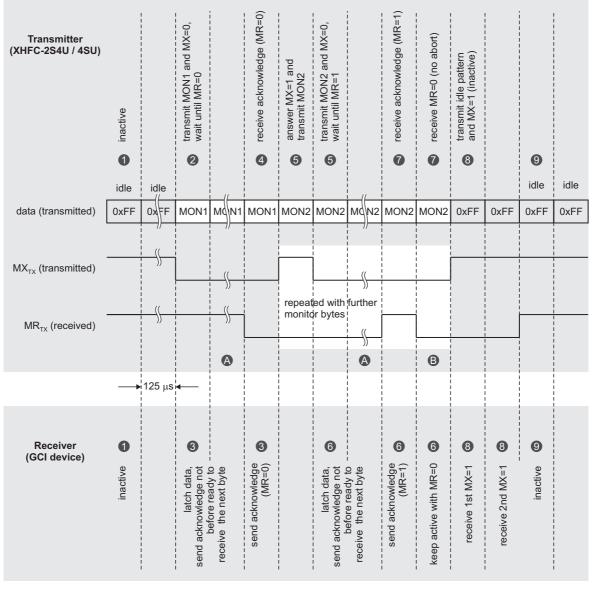

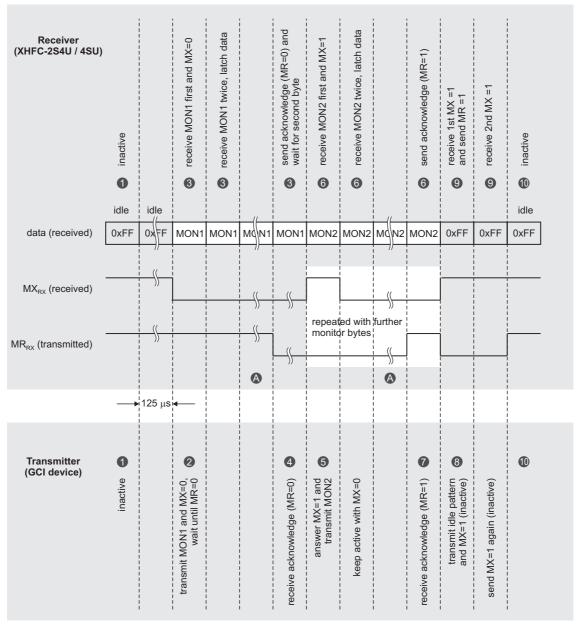

|   |     | 6.8.4   | GCI protocol                                                          | 1 |

|   |     |         | 6.8.4.1 XHFC-2S4U / XHFC-4SUtransmit procedure                        | 1 |

|   |     |         | 6.8.4.2 XHFC-2S4U / XHFC-4SUreceive procedure                         | 2 |

|   |     |         | 6.8.4.3 Receiver abort                                                | 4 |

|   | 6.9 | Registe | er description                                                        | 5 |

|   |     | 6.9.1   | Write only registers                                                  | 5 |

|   |     | 6.9.2   | Read only registers                                                   | 3 |

|   |     | 6.9.3   | Read / write register                                                 | 6 |

| - | ът  | • 141   |                                                                       | - |

| 7 |     |         | modulation (PWM) outputs 27                                           |   |

|   | 7.1 |         | ew                                                                    |   |

|   | 7.2 |         | rd PWM usage                                                          |   |

|   | 7.3 | Alterna | ative PWM usage                                                       | ð |

### Cologne Chip

|   | 7.4   | Registe                    | er descripti         | on                                                         | 279 |  |

|---|-------|----------------------------|----------------------|------------------------------------------------------------|-----|--|

| 8 | Bit F | Error Rate Test (BERT) 281 |                      |                                                            |     |  |

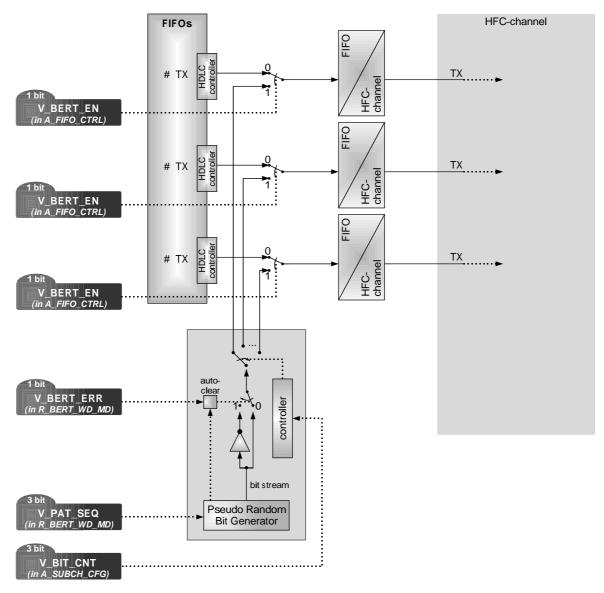

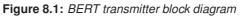

|   | 8.1   | BERT                       | functionali          | ty                                                         | 282 |  |

|   | 8.2   | BERT                       | transmitter          |                                                            | 282 |  |

|   | 8.3   | BERT                       | receiver .           |                                                            | 282 |  |

|   | 8.4   | Registe                    | er descripti         | on                                                         | 286 |  |

|   |       | 8.4.1                      | Write onl            | y registers                                                | 286 |  |

|   |       | 8.4.2                      | Read only            | v registers                                                | 287 |  |

| 9 | Cloc  | k, PLL                     | , reset, into        | errupt, timer and watchdog 2                               | .89 |  |

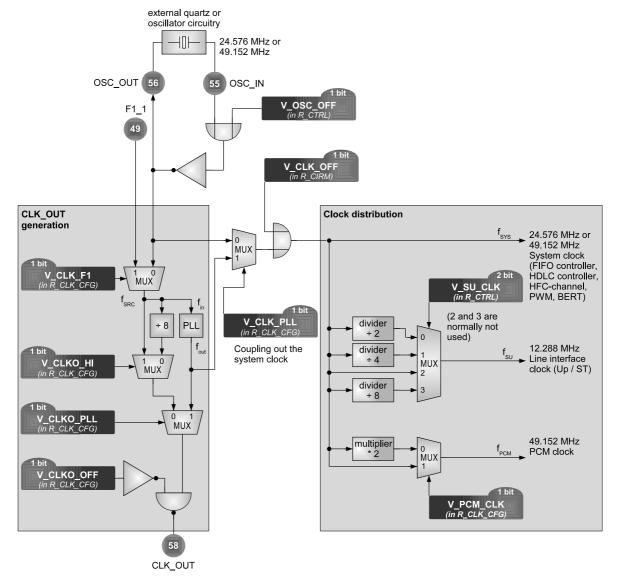

|   | 9.1   | Clock                      |                      |                                                            | 290 |  |

|   |       | 9.1.1                      | Clock out            | put                                                        | 290 |  |

|   |       | 9.1.2                      | Clock dis            | -<br>tribution                                             | 290 |  |

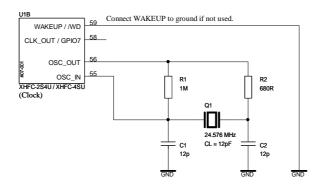

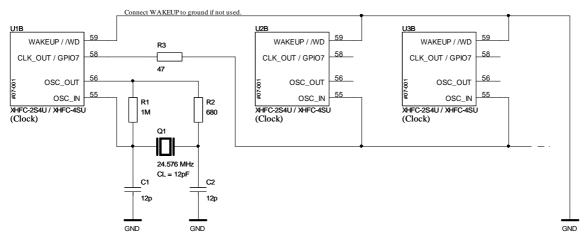

|   |       | 9.1.3                      | Clock osc            | illator circuitry                                          | .92 |  |

|   |       |                            | 9.1.3.1              | Frequency accuracy                                         | .92 |  |

|   |       |                            | 9.1.3.2              | Pierce oscillator                                          | .92 |  |

|   |       |                            | 9.1.3.3              | 3rd overtone oscillator                                    | .93 |  |

|   |       |                            | 9.1.3.4              | Crystal oscillator circuitry                               | .93 |  |

|   |       |                            | 9.1.3.5              | Several XHFC-2S4U/4SU with a single oscillator circuitry 2 | .93 |  |

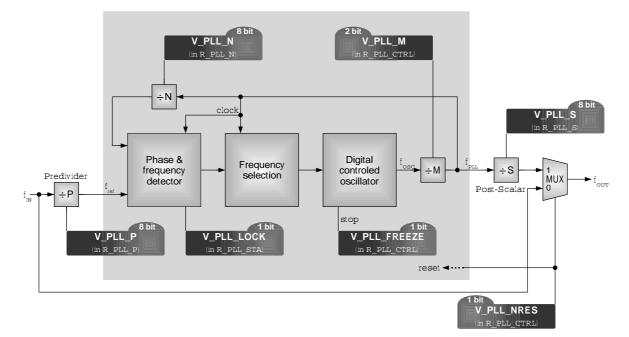

|   | 9.2   | Phase 1                    | locked loop          | (PLL)                                                      | .95 |  |

|   |       | 9.2.1                      | Overview             |                                                            | .95 |  |

|   |       | 9.2.2                      | PLL struc            | ture                                                       | .95 |  |

|   |       | 9.2.3                      | PLL oper             | ation                                                      | .96 |  |

|   |       | 9.2.4                      | Supply no            | bise requirements for PLL locking                          | .96 |  |

|   |       | 9.2.5                      | PLL conf             | iguration                                                  | .97 |  |

|   | 9.3   | Reset                      |                      |                                                            | 00  |  |

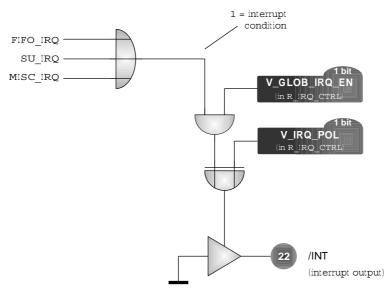

|   | 9.4   | Interru                    | pt                   |                                                            | 801 |  |

|   |       | 9.4.1                      | Common               | features                                                   | 801 |  |

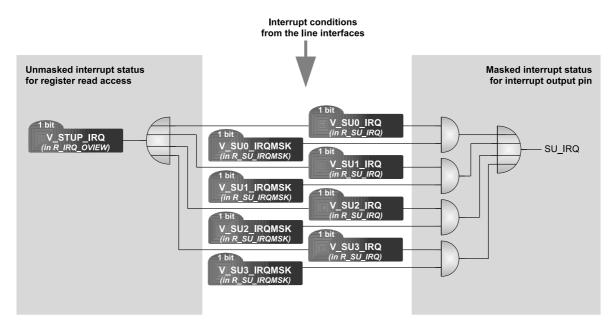

|   |       | 9.4.2                      | ST/U <sub>p</sub> in | terface interrupt                                          | 801 |  |

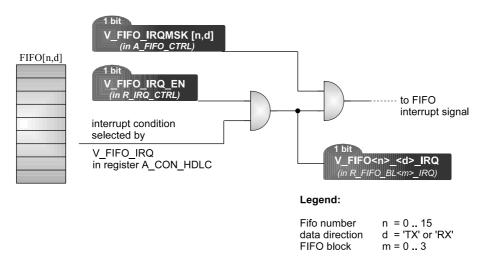

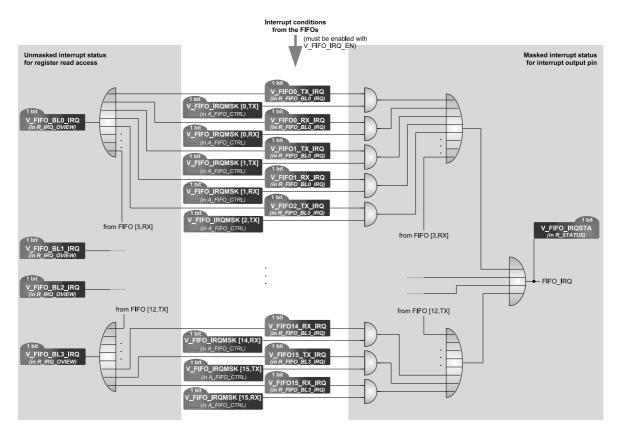

|   |       | 9.4.3                      | FIFO inte            | rrupt                                                      | 801 |  |

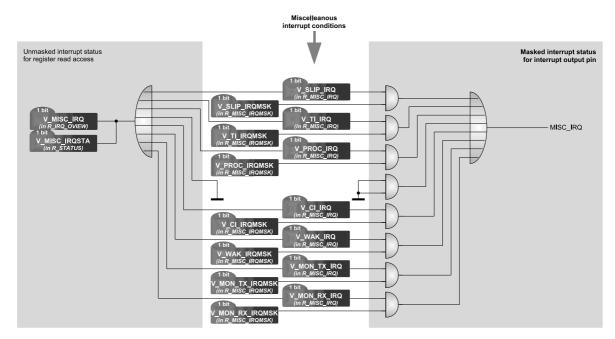

|   |       | 9.4.4                      | Miscellea            | nous interrupts                                            | 803 |  |

|   |       |                            | 9.4.4.1              | Line interface frequency slip interrupt                    | 803 |  |

|   |       |                            | 9.4.4.2              | Timer interrupt                                            | 604 |  |

|   |       |                            | 9.4.4.3              | Processing / non-processing interrupt                      | 604 |  |

|   |       |                            | 9.4.4.4              | Command / indication interrupt (GCI interface)             | 805 |  |

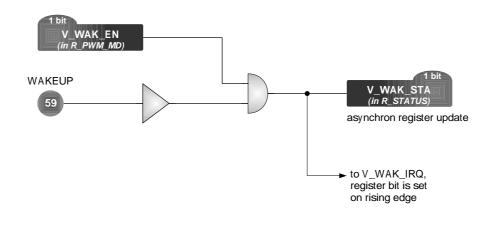

|   |       |                            | 9.4.4.5              | _                                                          | 805 |  |

|   |       |                            | 9.4.4.6              | Interrupt for GCI monitor byte transmission                | 805 |  |

|   |       |                            | 9.4.4.7              | Interrupt after GCI monitor byte received                  | 805 |  |

|     | 9.5                                         | Watchdog reset                              | 307 |  |  |  |

|-----|---------------------------------------------|---------------------------------------------|-----|--|--|--|

|     | 9.6                                         | Register description                        | 308 |  |  |  |

|     |                                             | 9.6.1 Write only registers                  | 308 |  |  |  |

|     |                                             | 9.6.2 Read only registers                   | 316 |  |  |  |

|     |                                             | 9.6.3 Read / write registers                | 325 |  |  |  |

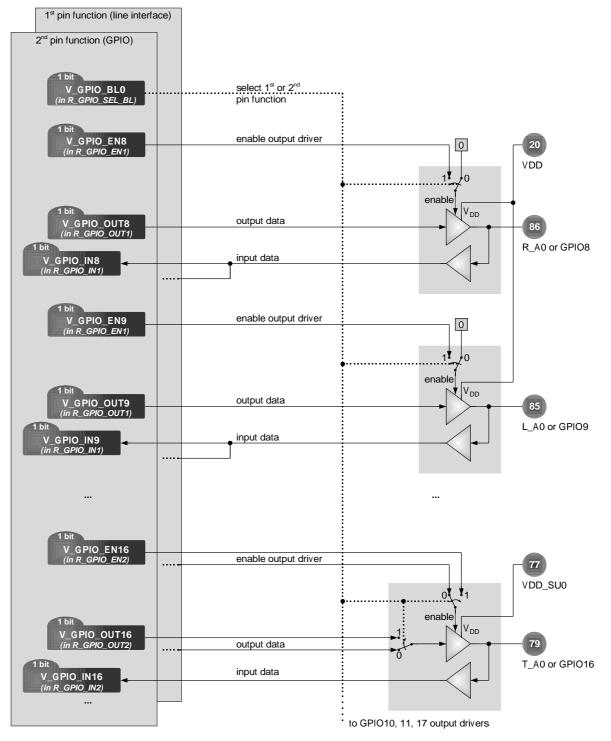

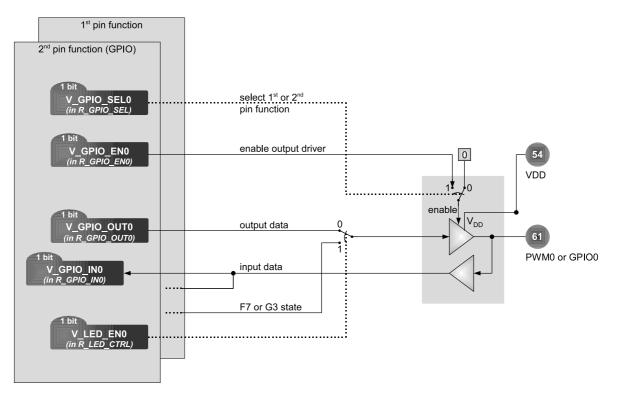

| 10  | Gene                                        | eral purpose I/O pins (GPIO)                | 327 |  |  |  |

|     | 10.1                                        | GPIO functionality                          | 328 |  |  |  |

|     | 10.2                                        | GPIO output voltage                         | 328 |  |  |  |

|     | 10.3                                        | Activation state F7 / G3 signalling         | 331 |  |  |  |

|     | 10.4                                        | Register description                        | 333 |  |  |  |

|     |                                             | 10.4.1 Write only registers                 | 333 |  |  |  |

|     |                                             | 10.4.2 Read only registers                  | 342 |  |  |  |

| 11  | Elect                                       | trical characteristics                      | 345 |  |  |  |

| 12  | XHF                                         | FC-2S4U / XHFC-4SU package dimensions       | 349 |  |  |  |

| 13  | XHF                                         | FC-2S4U / XHFC-4SU address decoding erratum | 351 |  |  |  |

|     | 13.1                                        | Fault description                           | 352 |  |  |  |

|     | 13.2                                        | Work-Around                                 | 352 |  |  |  |

| Re  | feren                                       | ces                                         | 357 |  |  |  |

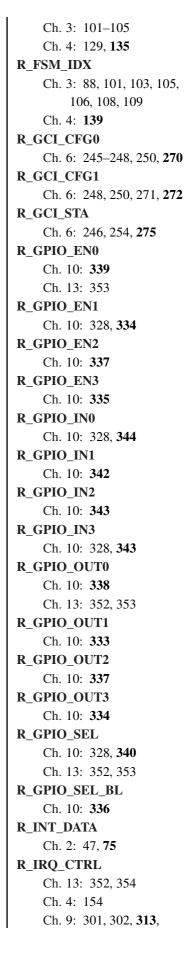

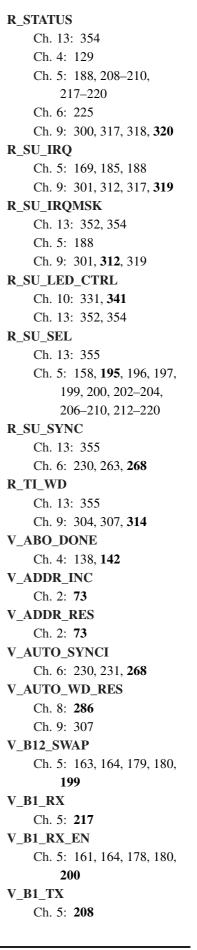

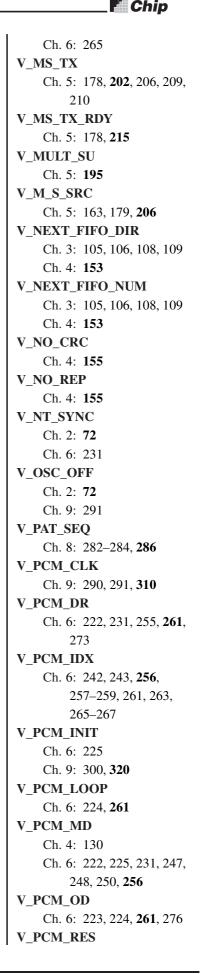

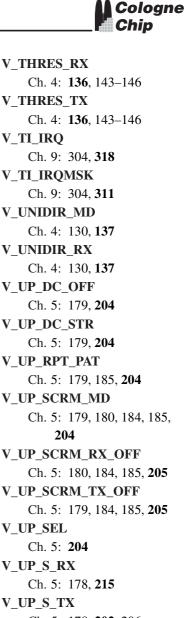

| Lis | List of register and bitmap abbreviations 3 |                                             |     |  |  |  |

# **List of Figures**

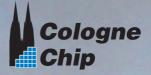

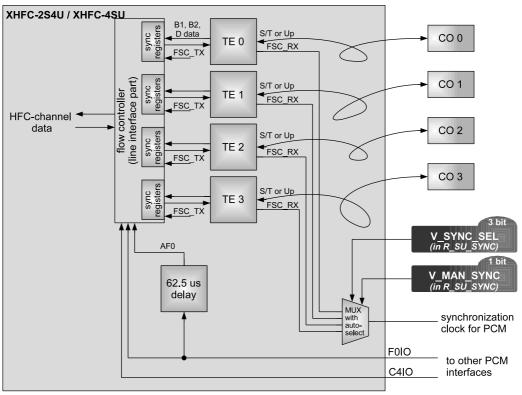

| 1.1  | XHFC-4SU block diagram                                                            | 31 |

|------|-----------------------------------------------------------------------------------|----|

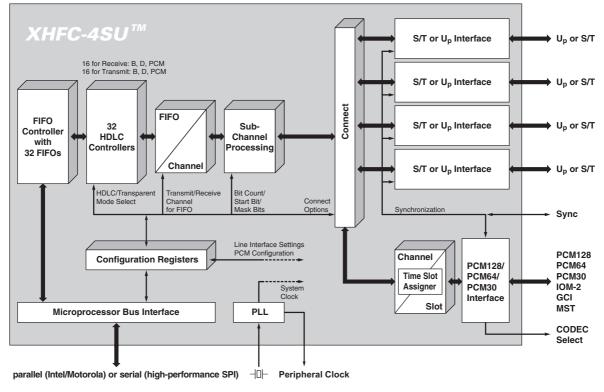

| 1.2  | XHFC-2S4U block diagram                                                           | 32 |

| 1.3  | XHFC-4SU pinout in parallel processor interface mode                              | 34 |

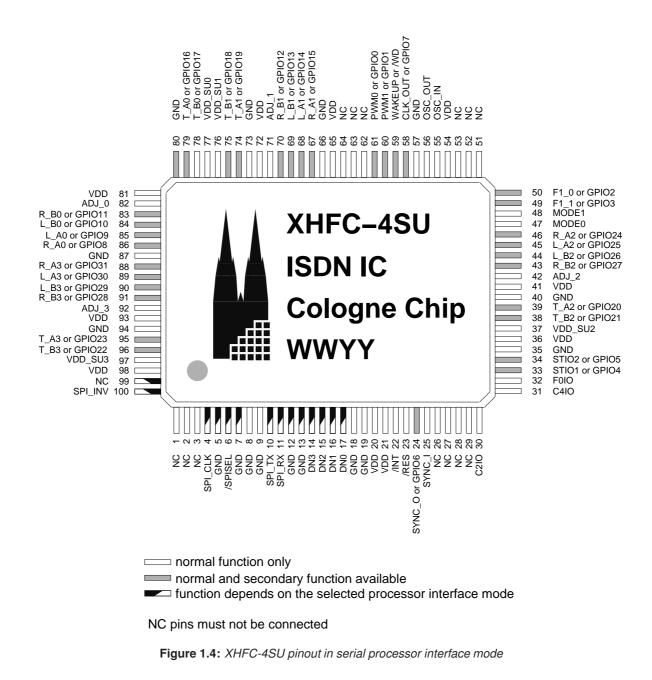

| 1.4  | XHFC-4SU pinout in serial processor interface mode                                | 35 |

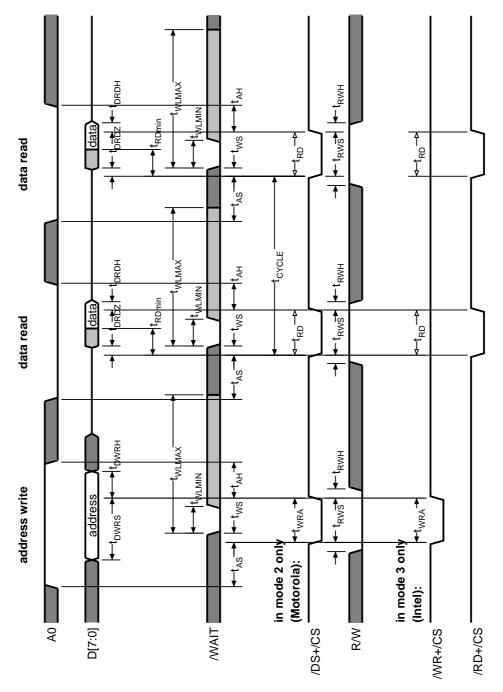

| 2.1  | Bus interface read access in mode 2 (Motorola) and mode 3 (Intel)                 | 48 |

| 2.2  | Bus interface write access in mode 2 (Motorola) and mode 3 (Intel)                | 51 |

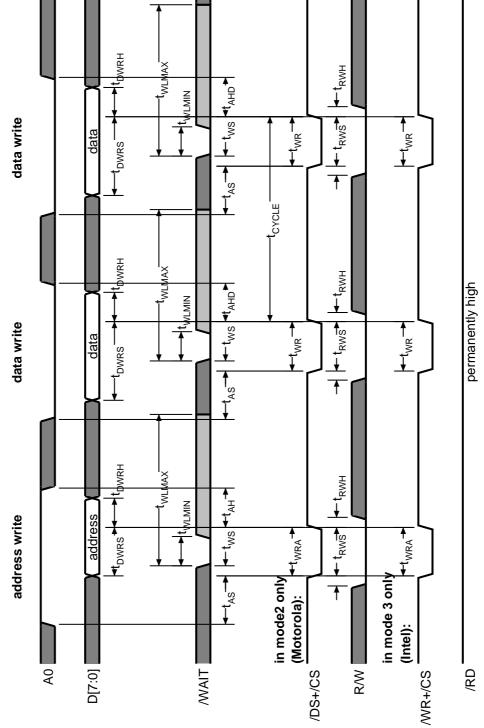

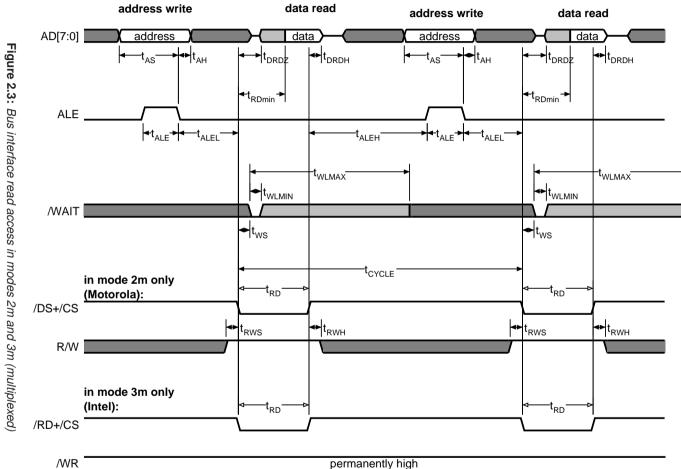

| 2.3  | Bus interface read access in modes 2m and 3m (multiplexed)                        | 54 |

| 2.4  | Bus interface write access in mode 2m and 3m (multiplexed)                        | 56 |

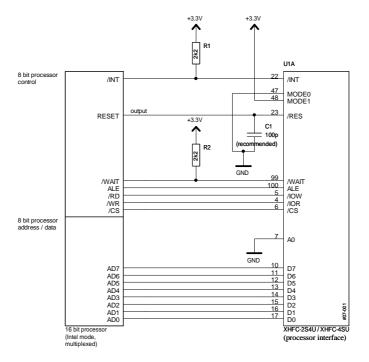

| 2.5  | 8 bit Motorola processor circuitry example (mode 2)                               | 57 |

| 2.6  | 8 bit Motorola processor circuitry example (mode 2m)                              | 57 |

| 2.7  | 8 bit Intel processor circuitry example (mode 3)                                  | 58 |

| 2.8  | 8 bit Intel processor circuitry example (mode 3m)                                 | 58 |

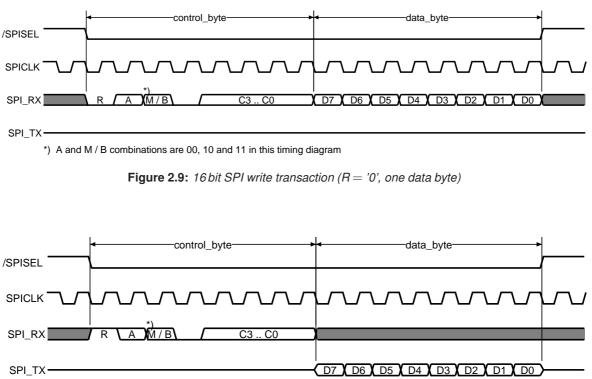

| 2.9  | 16 bit SPI write transaction ( $R = '0'$ , one data byte) $\ldots$                | 61 |

| 2.10 | 16 bit SPI read transaction ( $R = '1'$ , one data byte)                          | 61 |

| 2.11 | 40 bit SPI write transaction ( $R = '0'$ , four data bytes)                       | 62 |

| 2.12 | 40 bit SPI read transaction ( $R = '1'$ , four data bytes)                        | 62 |

| 2.13 | Split 40 bit SPI read transaction $(R = '1')$                                     | 62 |

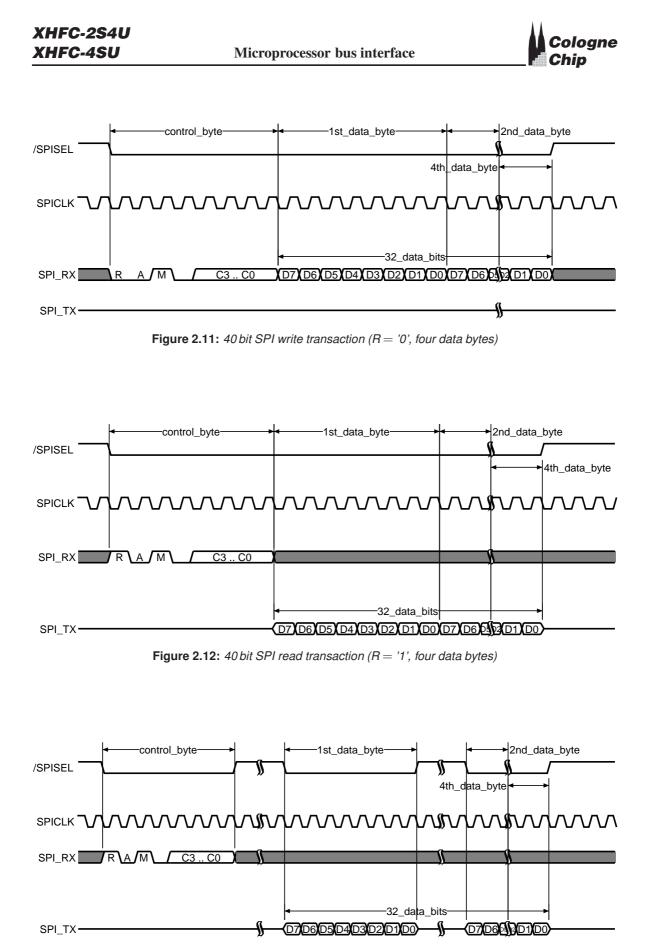

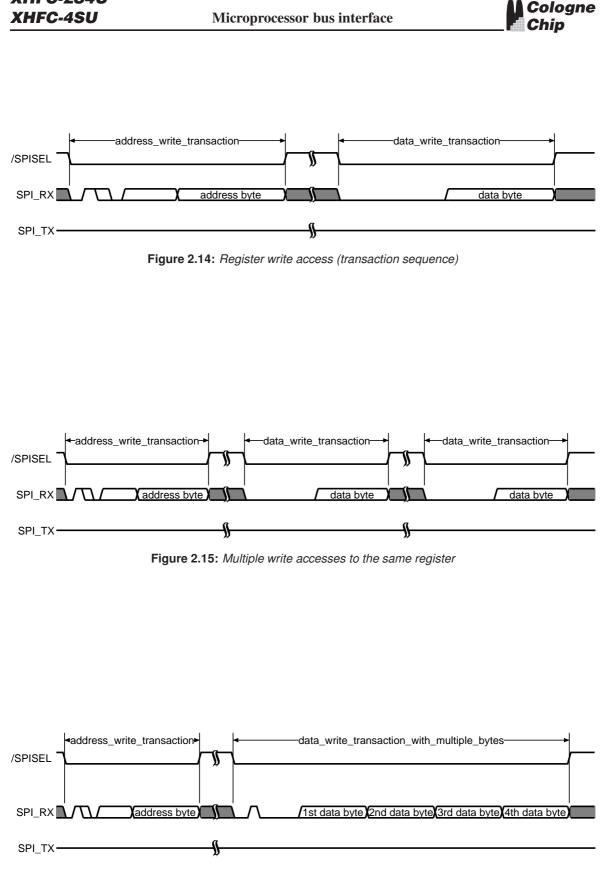

| 2.14 | Register write access (transaction sequence)                                      | 64 |

| 2.15 | Multiple write accesses to the same register                                      | 64 |

| 2.16 | Register write access with a 40 bit transaction                                   | 64 |

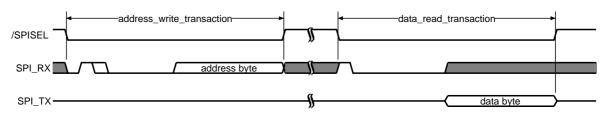

| 2.17 | Register read access (transaction sequence)                                       | 65 |

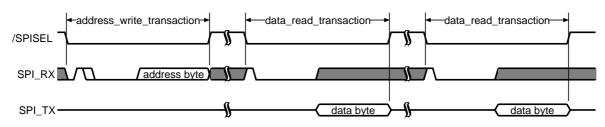

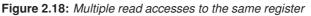

| 2.18 | Multiple read accesses to the same register                                       | 66 |

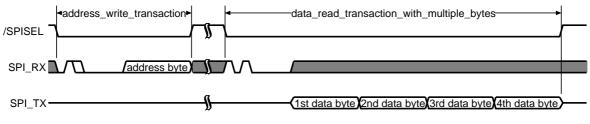

| 2.19 | Register read access with a 40 bit transaction                                    | 66 |

| 2.20 | SPI timing diagram for data write transactions                                    | 67 |

| 2.21 | SPI timing diagram for data read transactions                                     | 68 |

| 2.22 | SPI connection circuitry                                                          | 70 |

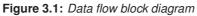

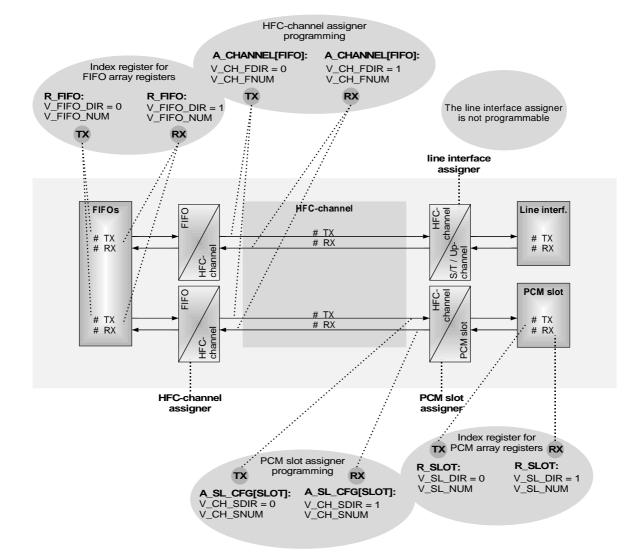

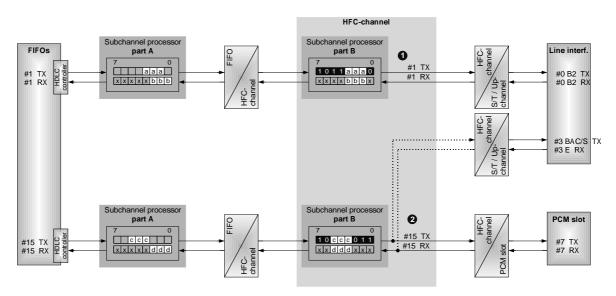

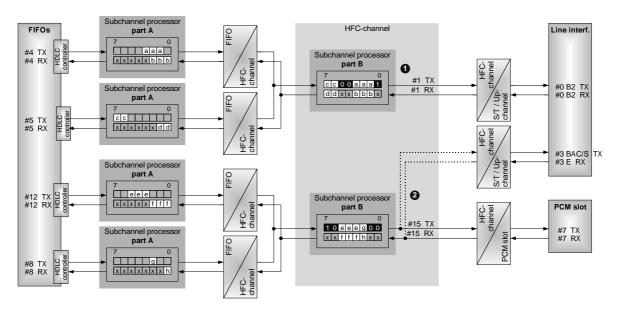

| 3.1  | Data flow block diagram                                                           | 77 |

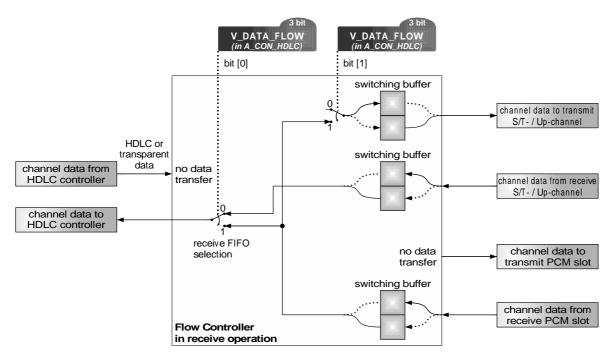

| 3.2  | Areas of FIFO oriented, HFC-channel oriented and PCM time slot oriented numbering | 79 |

|      |                                                                                   |    |

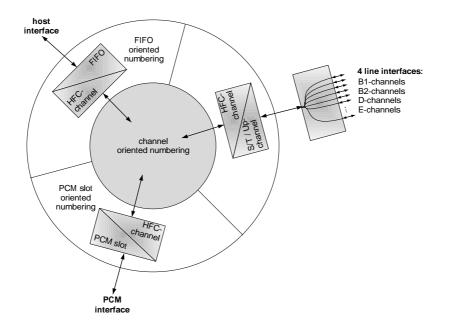

| 3.3                                                                                                                  | The flow controller in transmit operation                                                       | 81                                                                                                                                           |

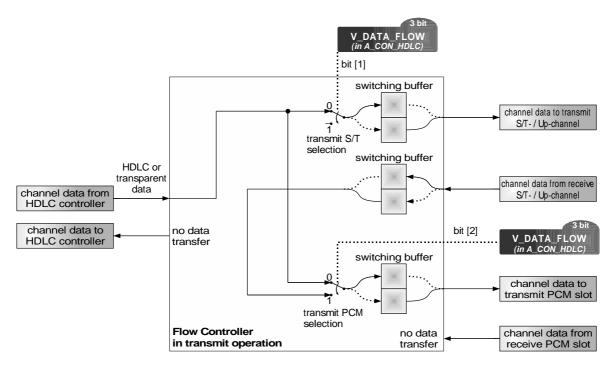

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 3.4                                                                                                                  | The flow controller in receive FIFO operation                                                   | 82                                                                                                                                           |

| 3.5                                                                                                                  | Overview of the assigner programming                                                            | 86                                                                                                                                           |

| 3.6                                                                                                                  | SM example                                                                                      | 90                                                                                                                                           |

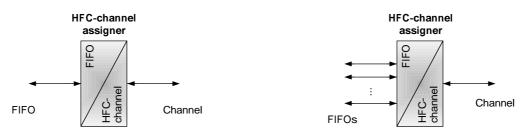

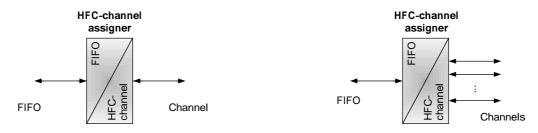

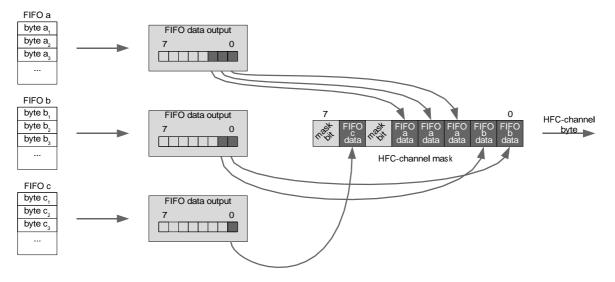

| 3.7                                                                                                                  | HFC-channel assigner in CSM                                                                     | 95                                                                                                                                           |

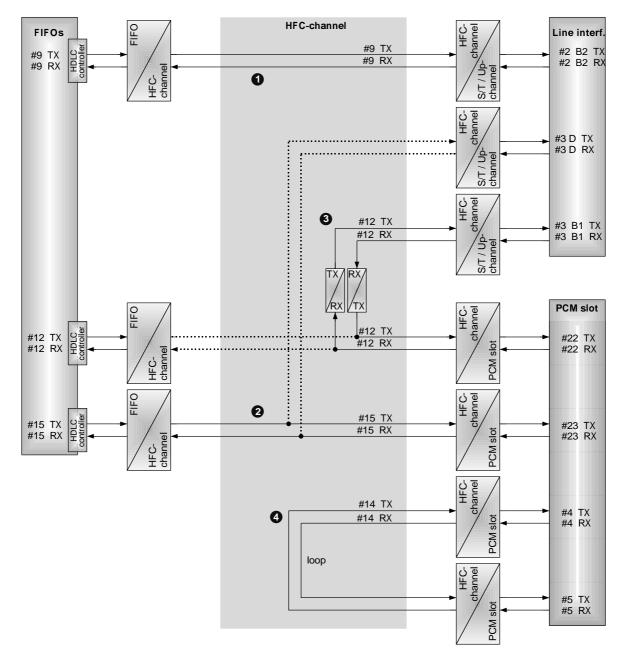

| 3.8                                                                                                                  | CSM example                                                                                     | 96                                                                                                                                           |

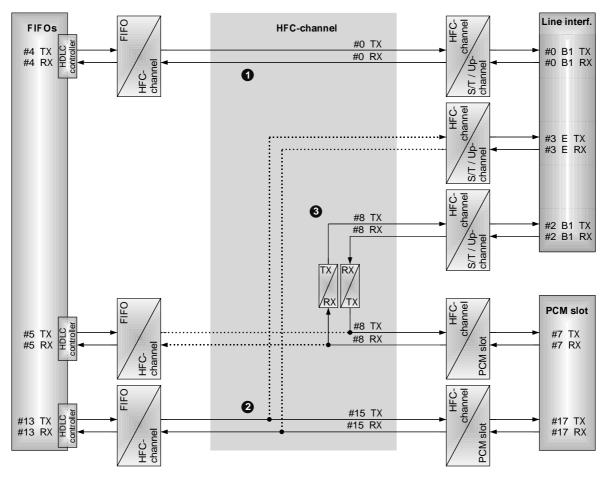

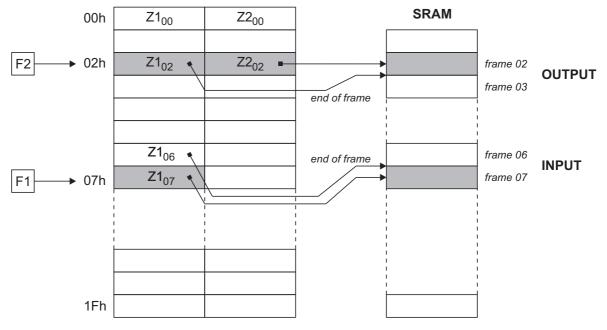

| 3.9                                                                                                                  | HFC-channel assigner in FSM                                                                     | 101                                                                                                                                          |

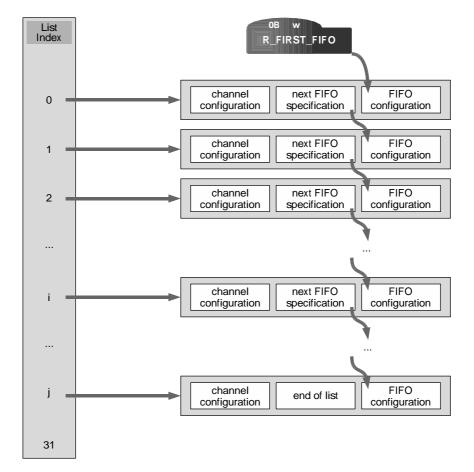

| 3.10                                                                                                                 | FSM list processing                                                                             | 102                                                                                                                                          |

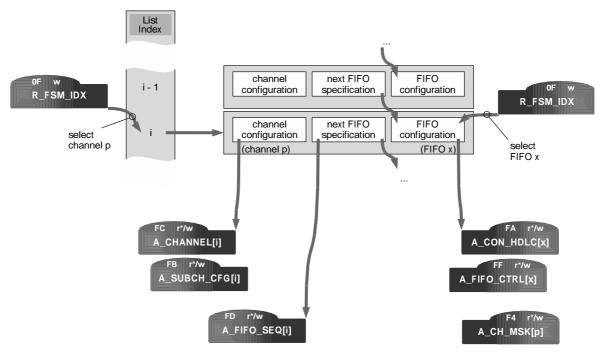

| 3.11                                                                                                                 | FSM list programming                                                                            | 103                                                                                                                                          |

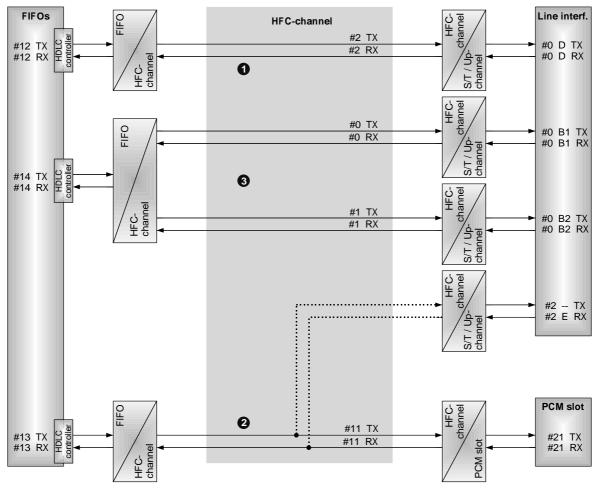

| 3.12                                                                                                                 | FSM example                                                                                     | 104                                                                                                                                          |

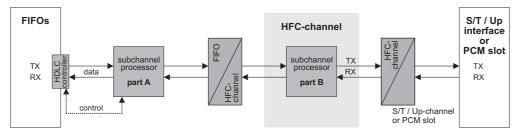

| 3.13                                                                                                                 | General structure of the subchannel processor                                                   | 110                                                                                                                                          |

| 3.14                                                                                                                 | Location of the subchannel parts A and B in the data flow diagram $\ldots \ldots \ldots \ldots$ | 110                                                                                                                                          |

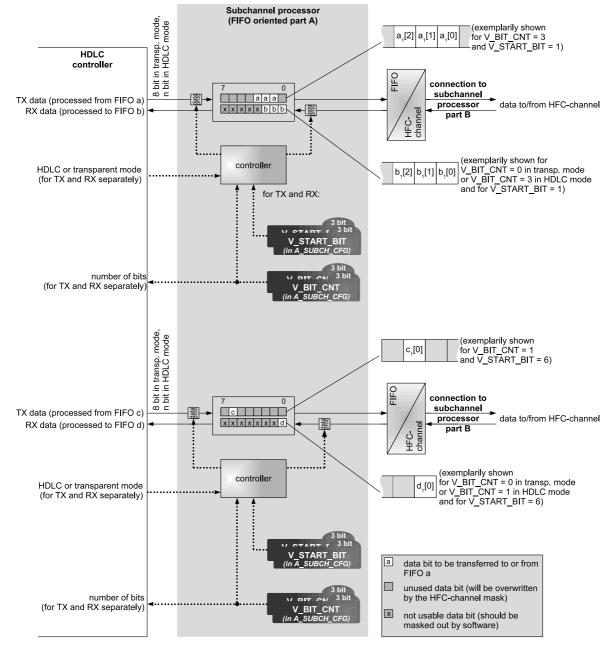

| 3.15                                                                                                                 | Part A of the subchannel processor                                                              | 112                                                                                                                                          |

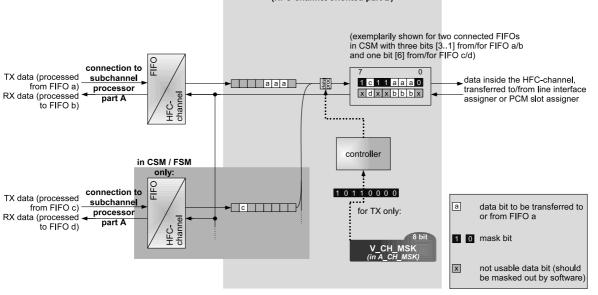

| 3.16                                                                                                                 | Part B of the subchannel processor                                                              | 114                                                                                                                                          |

| 3.17                                                                                                                 | SM example with subchannel processor                                                            | 115                                                                                                                                          |

| 3.18                                                                                                                 | CSM example with subchannel processor                                                           | 120                                                                                                                                          |

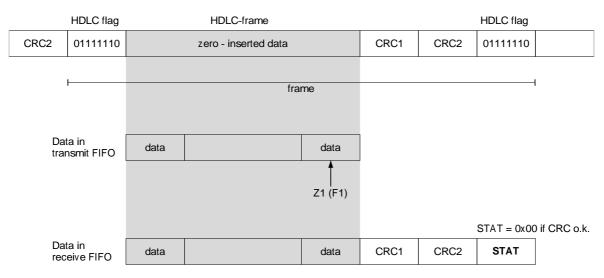

| 4.1                                                                                                                  | FIFO organization                                                                               | 131                                                                                                                                          |

| 4.2                                                                                                                  | FIFO data organization in HDLC mode                                                             | 132                                                                                                                                          |

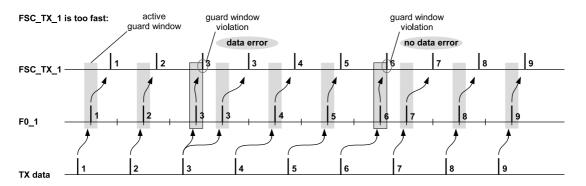

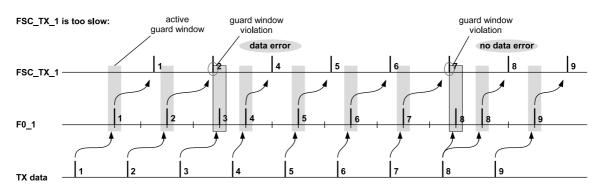

|                                                                                                                      |                                                                                                 |                                                                                                                                              |

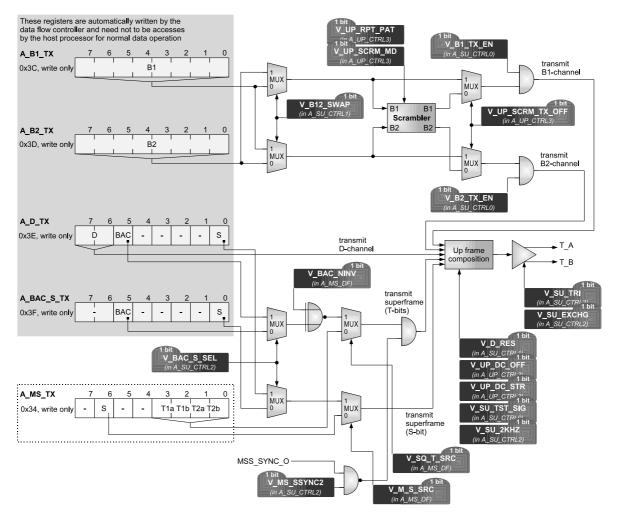

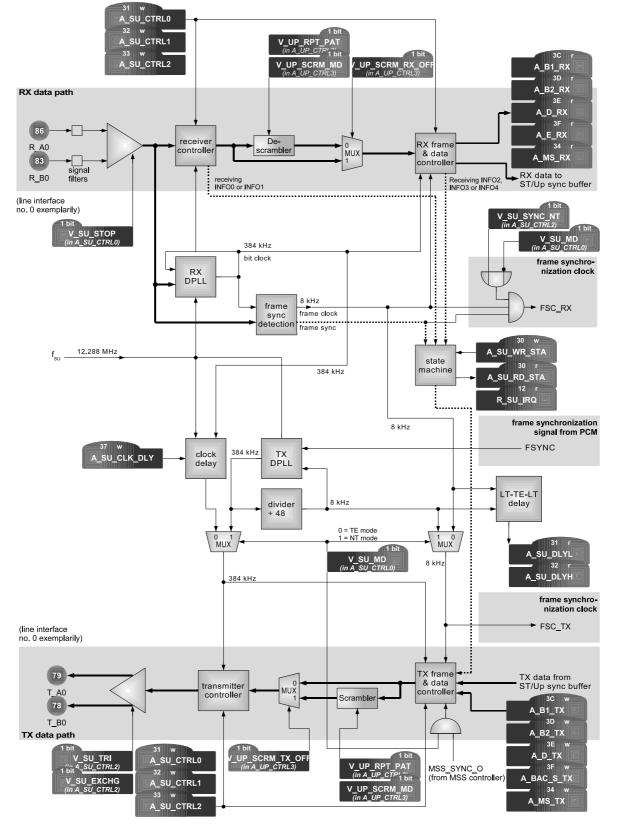

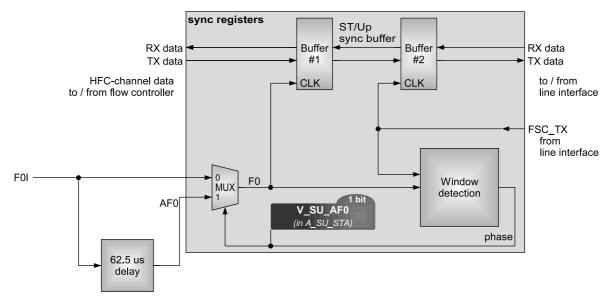

| 5.1                                                                                                                  | Overview of the Universal ISDN Port module                                                      | 159                                                                                                                                          |

| 5.1<br>5.2                                                                                                           | Overview of the Universal ISDN Port module                                                      | 159<br>160                                                                                                                                   |

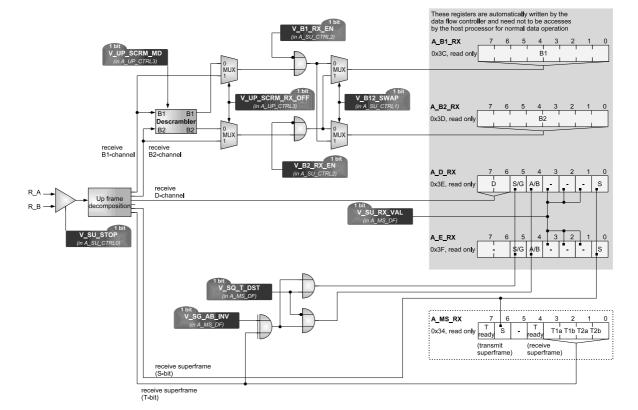

|                                                                                                                      |                                                                                                 |                                                                                                                                              |

| 5.2                                                                                                                  | Frame structure at reference point S and T                                                      | 160                                                                                                                                          |

| 5.2<br>5.3                                                                                                           | Frame structure at reference point S and T                                                      | 160<br>163                                                                                                                                   |

| <ul><li>5.2</li><li>5.3</li><li>5.4</li></ul>                                                                        | Frame structure at reference point S and T                                                      | 160<br>163<br>164                                                                                                                            |

| <ul><li>5.2</li><li>5.3</li><li>5.4</li><li>5.5</li></ul>                                                            | Frame structure at reference point S and T                                                      | 160<br>163<br>164<br>169<br>170                                                                                                              |

| <ul> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> </ul>                                          | Frame structure at reference point S and T                                                      | 160<br>163<br>164<br>169<br>170<br>171                                                                                                       |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                                                               | Frame structure at reference point S and T                                                      | 160<br>163<br>164<br>169<br>170<br>171<br>172                                                                                                |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                                                                 | Frame structure at reference point S and T                                                      | 160<br>163<br>164<br>169<br>170<br>171<br>172<br>172                                                                                         |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10                                                         | Frame structure at reference point S and T                                                      | 160<br>163<br>164<br>169<br>170<br>171<br>172<br>172<br>177                                                                                  |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                                                 | Frame structure at reference point S and T                                                      | <ol> <li>160</li> <li>163</li> <li>164</li> <li>169</li> <li>170</li> <li>171</li> <li>172</li> <li>172</li> <li>177</li> <li>179</li> </ol> |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12                                         | Frame structure at reference point S and T                                                      | <ol> <li>160</li> <li>163</li> <li>164</li> <li>169</li> <li>170</li> <li>171</li> <li>172</li> <li>172</li> <li>177</li> <li>179</li> </ol> |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13                                 | Frame structure at reference point S and T                                                      | 160<br>163<br>164<br>169<br>170<br>171<br>172<br>172<br>177<br>179<br>180                                                                    |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14                         | Frame structure at reference point S and T                                                      | 160<br>163<br>164<br>169<br>170<br>171<br>172<br>172<br>177<br>179<br>180<br>185                                                             |

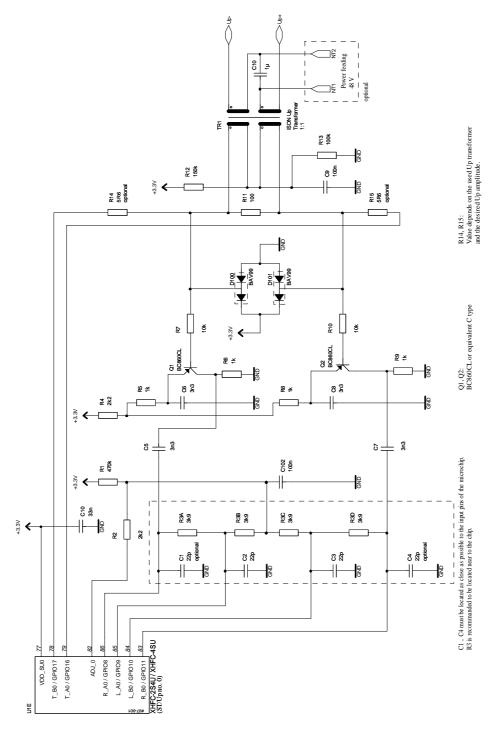

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15                 | Frame structure at reference point S and T                                                      | 160<br>163<br>164<br>169<br>170<br>171<br>172<br>172<br>177<br>179<br>180<br>185<br>186                                                      |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16         | Frame structure at reference point S and T                                                      | 160<br>163<br>164<br>169<br>170<br>171<br>172<br>172<br>177<br>179<br>180<br>185<br>186<br>189                                               |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17 | Frame structure at reference point S and T                                                      | 160<br>163<br>164<br>169<br>170<br>171<br>172<br>172<br>172<br>177<br>179<br>180<br>185<br>186<br>189<br>190<br>191                          |

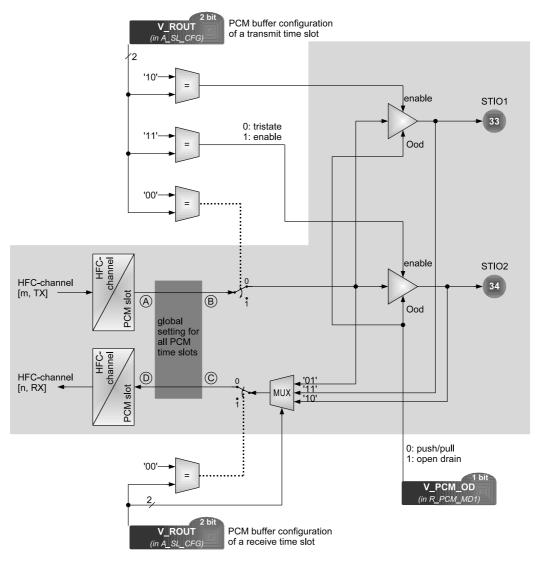

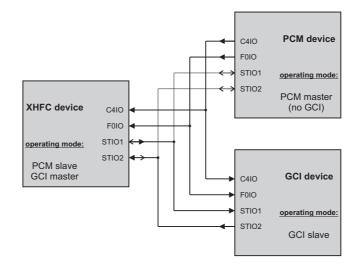

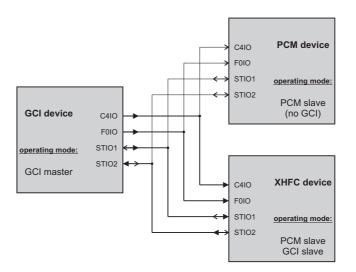

| 6.1  | PCM data flow for transmit and receive time slots                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 223 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

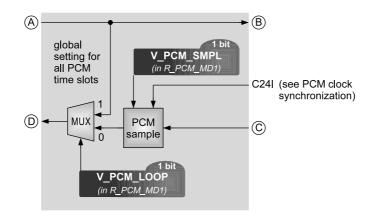

| 6.2  | Global setting for all PCM time slots (detail of Figure 6.1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 224 |

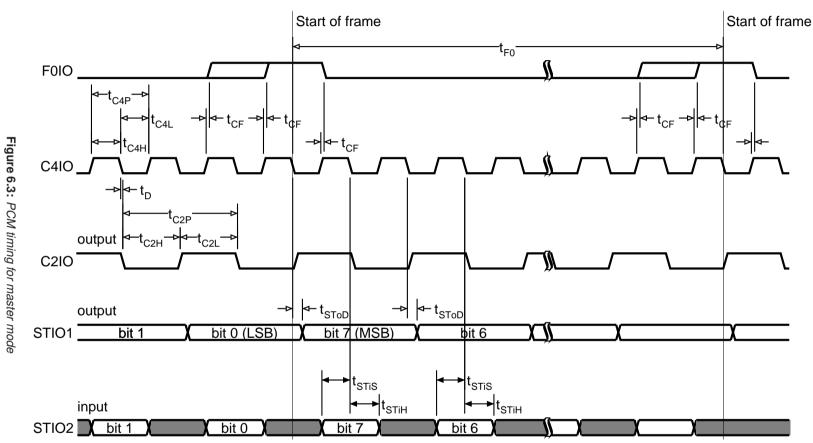

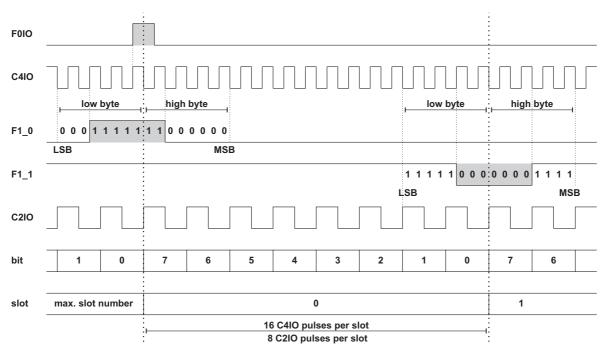

| 6.3  | PCM timing for master mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 226 |

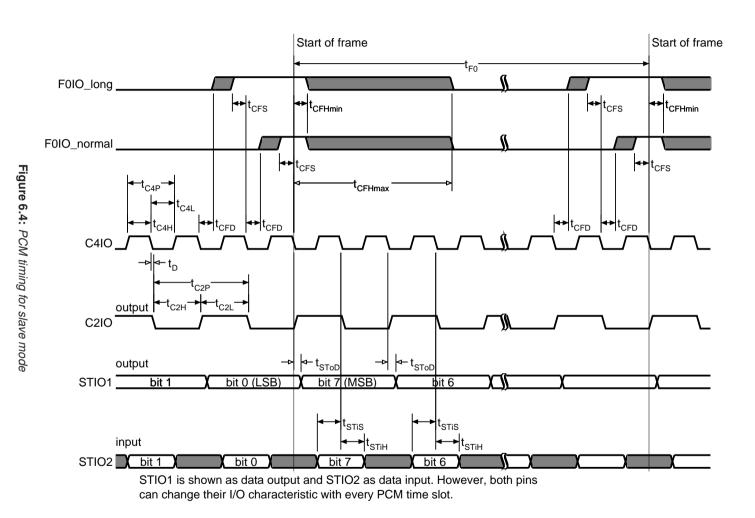

| 6.4  | PCM timing for slave mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 228 |