# Layer - 1 Conformance Test

for the S/T interface of XHFC - 1SU / XHFC - 2SU / XHFC - 2S4U / XHFC - 4SU ISDN Basic Rate Controllers

measured with S/T Port Line Interface Subassembly Revision 2 of the XHFC Evaluation Kit

Cologne Chip AG Eintrachtstrasse 113 D - 50668 Köln Germany

Tel.: +49 (0) 221 / 91 24-0 Fax: +49 (0) 221 / 91 24-100

http://www.CologneChip.com http://www.CologneChip.de support@CologneChip.com

Copyright 1994 - 2006 Cologne Chip AG All Rights Reserved

The information presented can not be considered as assured characteristics. Data can change without notice. Parts of the information presented may be protected by patent or other rights. Cologne Chip products are not designed, intended, or authorized for use in any application intended to support or sustain life, or for any other application in which the failure of the Cologne Chip product could create a situation where personal injury or death may occur.

## Contents

| 1 | Ove  | rview                                             | 5  |

|---|------|---------------------------------------------------|----|

| 2 | Out  | put impedance                                     | 6  |

| 3 | Puls | e shape                                           | 8  |

| 4 | Puls | e amplitude                                       | 11 |

| 5 | Puls | e unbalance of an isolated couple of pulses       | 12 |

| 6 | Trai | nsmitter output longitudinal conversion loss      | 13 |

| 7 | Reco | eiver input impedance                             | 14 |

| 8 | Reco | eiver longitudinal conversion loss                | 15 |

| 9 | Inpu | it to output offset                               | 16 |

|   | 9.1  | Config. I: Binary ones, different jitter          | 16 |

|   | 9.2  | Config. I: Octet 0x0AA, different jitter          | 17 |

|   | 9.3  | Config. I: Binary zeros, different jitter         | 18 |

|   | 9.4  | Config. I: $2^{19} - 1$ PRBS, different jitter    | 20 |

|   | 9.5  | Config. II: Binary ones, different jitter         | 21 |

|   | 9.6  | Config. II: Octet 0x0AA, different jitter         | 22 |

|   | 9.7  | Config. II: Binary zeros, different jitter        | 24 |

|   | 9.8  | Config. II: $2^{19} - 1$ PRBS, different jitter   | 25 |

|   | 9.9  | Config. IV: Binary ones, different jitter         | 26 |

|   | 9.10 | Config. IV: Octet 0x0AA, different jitter         | 28 |

|   | 9.11 | Config. IV: Binary zeros, different jitter        | 29 |

|   | 9.12 | Config. IV: $2^{19} - 1$ PRBS, different jitter   | 30 |

|   | 9.13 | Config. IIIa: Binary ones, different jitter       | 32 |

|   | 9.14 | Config. IIIa: Octet 0x0AA, different jitter       | 33 |

|   | 9.15 | Config. IIIa: Binary zeros, different jitter      | 34 |

|   | 9.16 | Config. IIIa: $2^{19} - 1$ PRBS, different jitter | 36 |

|   | 9.17 | Config. IIIb: Binary ones, different jitter       | 37 |

|   | 9.18 | Config. IIIb: Octet 0x0AA, different jitter       | 38 |

|   | 9.19 | Config. IIIb: Binary zeros, different jitter      | 40 |

|   | 9.20 | Config. IIIb: $2^{19} - 1$ PRBS, different jitter | 41 |

| 10 | Receiver sensitivity                                               | 43 |

|----|--------------------------------------------------------------------|----|

|    | 10.1 config. IIIa: 1.5 dB attenuated, different jitter             | 43 |

|    | 10.2 config. IIIa: 1.5 dB gain, different jitter                   | 44 |

|    | 10.3 config. IIIb: 1.5 dB attenuated, different jitter             | 45 |

|    | 10.4 config. IIIb: 1.5 dB gain, different jitter                   | 46 |

|    | 10.5 config. I: 1.5 dB attenuated, 200 kHz noise, different jitter | 47 |

|    | 10.6 config. I: 1.5 dB attenuated, 2 MHz noise, different jitter   | 48 |

|    | 10.7 config. II: 1.5 dB attenuated, different jitter               | 49 |

|    | 10.8 config. II: 1.5 dB gain, different jitter                     | 50 |

|    | 10.9 config. IV: 1.5 dB gain, different jitter                     | 51 |

| 11 | Jitter characteristics                                             | 52 |

|    | 11.1 Config. I: Different input sequences                          | 52 |

|    | 11.2 Config. II: Different input sequences                         | 53 |

|    | 11.3 Config. IV: Different input sequences                         | 54 |

|    | 11.4 Config. IIIa: Different input sequences                       | 55 |

|    | 11.5 Config. IIIb: Different input sequences                       | 56 |

| A  | S/T line interface schematic                                       | 57 |

| Re | ferences                                                           | 58 |

## 1 Overview

This document contains the test report and the measurement results for the S/T line interface of the single-port Basic Rate Controller IC XHFC-1SU [1] and the multi-port Basic Rate Controller ICs XHFC-2SU [3], XHFC-2S4U and XHFC-4SU [2] of Cologne Chip.

All measurements were executed with the XHFC-4SU Evaluation Board Revision 1 [5] with S/T Port Line Interface Subassembly Revision 2 [4] (please refer to schematic in appendix A on page 57). Both PCBs are part of the XHFC Series Evaluation Kit. The line interfaces of all XHFC series microchips are identical.

The device under test has successfully passed all layer 1 conformance tests according to the CTR 3/TBR 3 [6] specification. The ISDN controller microchips of the XHFC series are compliant to the hardware specifications of the ISDN standards I.430 [7].

The ISDN S/T conformance test has been made at the test laboratory for telecom interfaces of the TÜV Rheinland Product Safety in Cologne, Germany in August 2006. The TÜV labs are a certified body for Telecom Approvals. All tests were made using a Tektronix K 1403 conformance tester. The test results and measurement results shown in this document were saved from the test equipment on August 23h, 2006.

### **Test Laboratory**

| Name:           | TÜV Rheinland Product Safety GmbH<br>Section ISDN |

|-----------------|---------------------------------------------------|

| Street:         | Am Grauen Stein                                   |

| City:           | D - 51105 Koeln                                   |

| Country:        | Germany                                           |

| Contact Person: | Mr. Klaus Jauernik                                |

| Telephone:      | + 49 - 221 - 806 - 3428                           |

| Telefax:        | +49-221-806-1536                                  |

| e-mail:         | jauernik@de.tuv.com                               |

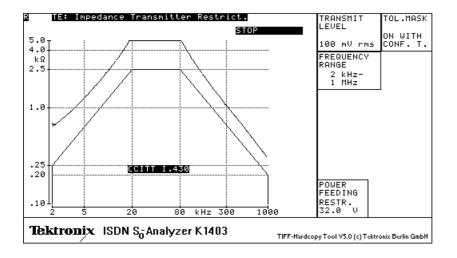

## 2 Output impedance

## V30-12.4

Test A: Output impedance when transmitting a binary one in state F3, restricted power at 32 V.

Conformance PASSED

Measurement finished. Expected TAV-count reached.

## 30-12.8

Test B: Output impedance when transmitting a binary zero, positive pulses into a 50  $\Omega$  load, restricted power at 32 V.

Double pulses into  $50 \Omega$  (R+,R-,R+-), isolated pulses (R+) w. loop.

Conformance PASSED

| $R(+/-) = 0.000000 \Omega \qquad R(+) = 0.000000 \Omega \qquad R(-) = 37.969784 \Omega$ |

|-----------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------|

Measurement finished. Expected TAV-count reached.

## V30-12.12

Test B: Output impedance when transmitting a binary zero, negative pulses into a 50  $\Omega$  load, restricted power at 32 V.

Double pulses into  $50 \Omega$  (R+,R-,R+-), isolated pulses (R-) w. loop.

Conformance PASSED

| $R(+/-) = 0.000000 \Omega$ | $R(+) = 37.852459 \Omega$ | $R(-) = 0.000000 \Omega$ |

|----------------------------|---------------------------|--------------------------|

|----------------------------|---------------------------|--------------------------|

## V30-12.16

Test B: Output impedance when transmitting a binary zero, positive pulses into a  $400 \Omega$  load, restricted power at 32 V.

Double pulses into  $400 \Omega$  (R+,R-,R+-), isolated pulses (R+) w. loop.

Conformance PASSED

| $R(+/-) = 0.000000 \Omega$ | $R(+) = 0.000000 \Omega$ | $R(-) = 39.043797 \Omega$ |

|----------------------------|--------------------------|---------------------------|

|----------------------------|--------------------------|---------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-12.20

Test B: Output impedance when transmitting a binary zero, negative pulses into a 400  $\Omega$  load, restricted power at 32 V.

Double pulses into  $400 \Omega$  (R+,R-,R+-), isolated pulses (R-) w. loop.

Conformance PASSED

| $R(+/-) = 0.000000 \Omega$ | $R(+) = 38.720039 \Omega$ | $R(-) = 0.000000 \Omega$ |

|----------------------------|---------------------------|--------------------------|

|----------------------------|---------------------------|--------------------------|

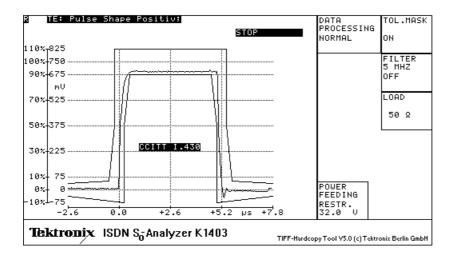

## **3** Pulse shape

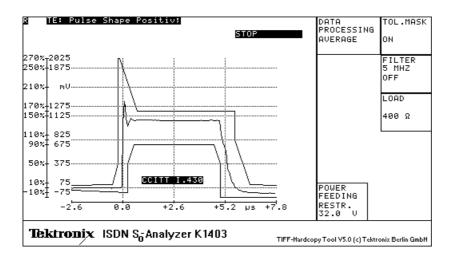

## V30-13.4

Pulse shape and amplitude for positive pulses, restricted power at 32 V.

Multi Periodic Sampling (MPS), 12Bit/24MHz and 1<sup>st</sup> double pulse, 12Bit/16MHz (#).

Conformance PASSED

Measurement finished. Expected TAV-count reached.

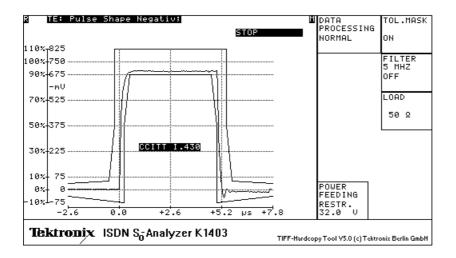

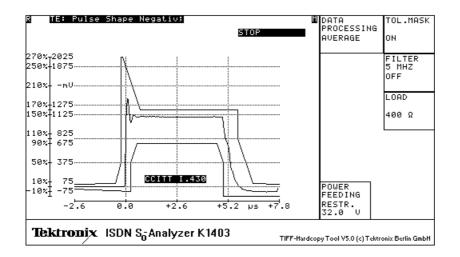

## V30-13.8

Pulse shape and amplitude for negative pulses, restricted power at 32 V.

Multi Periodic Sampling (MPS), 12 Bit/24 MHz and  $1^{st}$  double pulse, 12 Bit / 16 MHz (#).

Conformance PASSED

## V30-13.12

Test A: Voltage on a 400  $\Omega$  load (pulse shape) for positive pulses, restricted power at 32 V. Multi Periodic Sampling (MPS), 12 Bit/24 MHz.

Conformance PASSED

Measurement finished. Expected TAV-count reached.

#### V30-13.16

Test A: Voltage on a 400  $\Omega$  load (pulse shape) for negative pulses, restricted power at 32 V.

Multi Periodic Sampling (MPS), 12 Bit/24 MHz.

Conformance PASSED

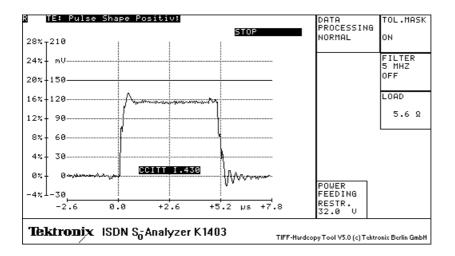

#### V30-13.20

Test B: Voltage on a 5.6  $\Omega$  load (pulse shape) for positive pulses, restricted power at 32 V. Multi Periodic Sampling (MPS), 12Bit/24MHz.

Conformance PASSED

Measurement finished. Expected TAV-count reached.

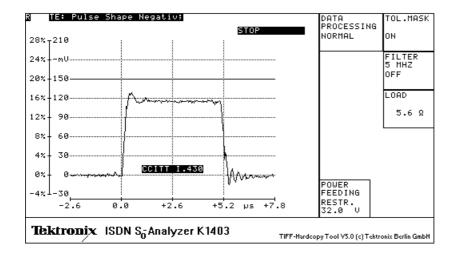

#### V30-13.24

Test B: Voltage on a 5.6  $\Omega$  load (pulse shape) for negative pulses, restricted power at 32 V.

Multi Periodic Sampling (MPS), 12Bit/24MHz.

Conformance PASSED

## 4 Pulse amplitude

## V30-14.1

Pulse amplitude, normal power at 42 V.

Multi Periodic Sampling (MPS), 12 Bit/16 MHz.

Conformance PASSED

| $\Delta U_+/U_{nom} = -7.607476\%$ | $\Delta U_{-}/U_{nom} = -8.184329\%$ |

|------------------------------------|--------------------------------------|

|------------------------------------|--------------------------------------|

Measurement finished. Expected TAV-count reached.

### V30-14.2

Pulse amplitude, normal power at 24 V

Multi Periodic Sampling (MPS), 12 Bit / 16 MHz.

Conformance PASSED

| $\Delta U_{+}/U_{nom} = -7.669433\% \qquad \qquad \Delta U_{-}/U_{nom} = -8.250562\%$ |

|---------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------|

Measurement finished. Expected TAV-count reached.

## V30-14.4

Pulse amplitude, restricted power at 32 V

Multi Periodic Sampling (MPS), 12 Bit / 16 MHz.

Conformance PASSED

| $\Delta dU_+/U_{nom} = -7.684175\%$ | $\Delta U_{-}/U_{nom} = -8.171725\%$ |

|-------------------------------------|--------------------------------------|

|-------------------------------------|--------------------------------------|

## 5 Pulse unbalance of an isolated couple of pulses

## V30-14.5

Pulse unbalance of an isolated couple of pulses, normal power at 42 V.

Multi Periodic Sampling (MPS),  $12\,\text{Bit}/16\,\text{MHz},$  digital integration of  $1^{\text{st}}$  or  $2^{\text{nd}}$  double pulse of INFO.

Conformance PASSED

$\Delta f/F_{nom} = -2.311680\%$

Measurement finished. Expected TAV-count reached.

### V30-14.6

Pulse unbalance of an isolated couple of pulses, normal power at 24 V.

Multi Periodic Sampling (MPS), 12 Bit/16 MHz, digital integration of  $1^{\text{st}}$  or  $2^{\text{nd}}$  double pulse of INFO.

Conformance PASSED

$\Delta f/F_{nom} = -3.158667\%$

Measurement finished. Expected TAV-count reached.

#### V30-14.8

Pulse unbalance of an isolated couple of pulses, restricted power at 32 V.

Multi Periodic Sampling (MPS), 12 Bit/16 MHz, digital integration of  $1^{\text{st}}$  or  $2^{\text{nd}}$  double pulse of INFO.

Conformance PASSED

$\Delta f/F_{nom} = -2.386763\%$

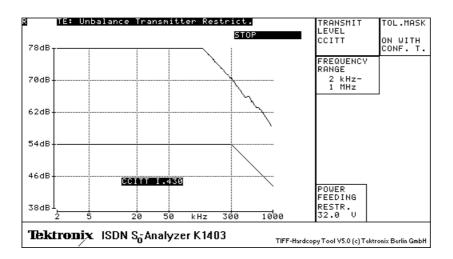

## 6 Transmitter output longitudinal conversion loss

## V30-15.1

Transmitter output longitudinal conversion loss in state F3, normal power at 42 V. Conformance PASSED

Measurement finished. Expected TAV-count reached.

### V30-15.2

Transmitter output longitudinal conversion loss in state F3, normal power at 24 V.

Conformance PASSED

Measurement finished. Expected TAV-count reached.

#### V30-15.3

Transmitter output longitudinal conversion loss in state F3, restricted power at 42 V.

Conformance PASSED

Measurement finished. Expected TAV-count reached.

#### V30-15.4

Transmitter output longitudinal conversion loss in state F3, restricted power at 32 V. Conformance PASSED

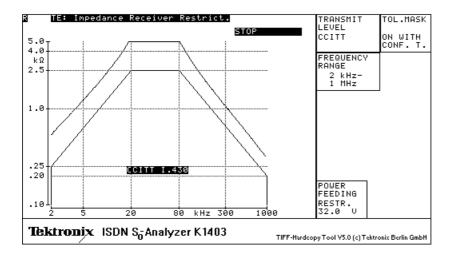

## 7 Receiver input impedance

## V30-16.4

Test A: Receiver input impedance in state F3, restricted power at 32 V.

Conformance PASSED

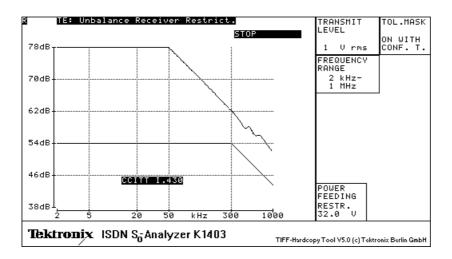

## 8 Receiver longitudinal conversion loss

### V30-18.1U

Receiver unbalance about earth (longitudinal conversion loss) in state F3, normal power at 42 V. Conformance PASSED

Measurement finished. Expected TAV-count reached.

#### V30-18.2U

Receiver unbalance about earth (longitudinal conversion loss) in state F3, normal power at 24 V.

Conformance PASSED

Measurement finished. Expected TAV-count reached.

#### V30-18.3U

Receiver unbalance about earth (longitudinal conversion loss) in state F3, restricted power at 42 V.

Conformance PASSED

Measurement finished. Expected TAV-count reached.

#### V30-18.4U

Receiver unbalance about earth (longitudinal conversion loss) in state F3, restricted power at 32 V. Conformance PASSED

Cologne Chip

## 9 Input to output offset

## 9.1 Config. I: Binary ones, different jitter

### V30-11.4a

Input to output offset, point to point configuration (high cap. cable with 6 dB attenuation) with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. I, jitter 5 Hz/0,5 UI

Conformance PASSED

| $t_{min} = -2.146405\%$ $t_{max} = 1.453641\%$ $t_{ava} = 1.053616\%$ |

|-----------------------------------------------------------------------|

|-----------------------------------------------------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.4b

Input to output offset, point to point configuration (high cap. cable with 6 dB attenuation) with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. I, jitter 20 Hz/0,125 UI

Conformance PASSED

| $t_{min} = -2.546384\%$ | $t_{max} = 1.453641\%$ | $t_{ava} = 0.653592\%$ |

|-------------------------|------------------------|------------------------|

|-------------------------|------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.4c

Input to output offset, point to point configuration (high cap. cable with 6 dB attenuation) with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. I, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = -2.346371\%$ | $t_{max} = 1.653653\%$ | $t_{ava} = -1.146381\%$ |

|-------------------------|------------------------|-------------------------|

|-------------------------|------------------------|-------------------------|

## V30-11.4d

Input to output offset, point to point configuration (high cap. cable with 6 dB attenuation) with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. I, jitter 2015 Hz/0,05 UI

Conformance PASSED

| $t_{min} = -3.546368\%$ | $t_{max} = 2.053616\%$ | $t_{ava} = -0.746371\%$ |

|-------------------------|------------------------|-------------------------|

|-------------------------|------------------------|-------------------------|

Measurement finished. Expected TAV-count reached.

## 9.2 Config. I: Octet 0x0AA, different jitter

#### V30-11.24a

Input to output offset, point to point configuration (high cap. cable with 6 dB attenuation) with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D-and D-Echo channels, restricted power at 32 V.

config. I, jitter 5 Hz/0,5 UI

Conformance PASSED

| $t_{min} = -1.946393\%$ | $t_{max} = 1.653653\%$ | $t_{ava} = -0.746371\%$ |

|-------------------------|------------------------|-------------------------|

|-------------------------|------------------------|-------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.24b

Input to output offset, point to point configuration (high cap. cable with 6 dB attenuation) with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D-and D-Echo channels, restricted power at 32 V.

config. I, jitter 20 Hz/0,125 UI

Conformance PASSED

| $t_{min} = -5.546376\%$ $t_{max} = -5.546376\%$ | $= 1.653653\% 	 t_{ava} = -0.346393\%$ |

|-------------------------------------------------|----------------------------------------|

|-------------------------------------------------|----------------------------------------|

## V30-11.24c

Input to output offset, point to point configuration (high cap. cable with 6 dB attenuation) with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D-and D-Echo channels, restricted power at 32 V.

config. I, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = -1.946393\%$ | $t_{max} = 1.653653\%$ | $t_{ava} = -1.146381\%$ |

|-------------------------|------------------------|-------------------------|

|-------------------------|------------------------|-------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.24d

Input to output offset, point to point configuration (high cap. cable with 6 dB attenuation) with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D-and D-Echo channels, restricted power at 32 V.

config. I, jitter 2015 Hz/0,05 UI

Conformance PASSED

| $t_{min} = -5.746388\%$ $t_{max} = 3.453641\%$ $t_{ava} = -0.546405\%$ | 746388% $t_{max} = 3.453641\%$ |

|------------------------------------------------------------------------|--------------------------------|

|------------------------------------------------------------------------|--------------------------------|

Measurement finished. Expected TAV-count reached.

## 9.3 Config. I: Binary zeros, different jitter

#### V30-11.44a

Input to output offset, point to point configuration (high cap. cable with 6 dB attenuation) with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. I, jitter 5 Hz/0,5 UI

Conformance PASSED

| $t_{min} = -1.546384\%$ $t_{max} = 2.053616\%$ $t_{ava} = -1.146381\%$ |  |

|------------------------------------------------------------------------|--|

|------------------------------------------------------------------------|--|

## V30-11.44b

Input to output offset, point to point configuration (high cap. cable with 6 dB attenuation) with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. I, jitter 20 Hz / 0,125 UI

Conformance PASSED

| $t_{min} = -1.946393\%$ | $t_{max} = 2.053616\%$ | $t_{ava} = 0.053616\%$ |

|-------------------------|------------------------|------------------------|

|                         |                        |                        |

Measurement finished. Expected TAV-count reached.

#### V30-11.44c

Input to output offset, point to point configuration (high cap. cable with 6 dB attenuation) with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. I, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = -2.546384\%$ $t_{max} = 1.853604\%$ $t_{ava} = 0.653592\%$ |

|-----------------------------------------------------------------------|

|-----------------------------------------------------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.44d

Input to output offset, point to point configuration (high cap. cable with 6 dB attenuation) with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. I, jitter 2015 Hz/0,05 UI

Conformance PASSED

| $t_{min} = -5.746388\%$ | $t_{max} = 1.853604\%$ | $t_{ava} = 0.653592\%$ |

|-------------------------|------------------------|------------------------|

|-------------------------|------------------------|------------------------|

## 9.4 Config. I: 2<sup>19</sup> – 1 PRBS, different jitter

## V30-11.64a

Input to output offset, point to point configuration (high cap. cable with 6 dB attenuation) with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. I, jitter 5 Hz/0,5 UI

Conformance PASSED

| $t_{min} = -2.346371\%$ | $t_{max} = 2.853604\%$ | $t_{ava} = 0.053616\%$ |

|-------------------------|------------------------|------------------------|

|                         |                        |                        |

Measurement finished. Expected TAV-count reached.

#### V30-11.64b

Input to output offset, point to point configuration (high cap. cable with 6 dB attenuation) with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. I, jitter 20 Hz/0,125 UI

Conformance PASSED

| $t_{min} = -2.546384\%$ | $t_{max} = 2.653592\%$ | $t_{ava} = -0.546405\%$ |

|-------------------------|------------------------|-------------------------|

|-------------------------|------------------------|-------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.64c

Input to output offset, point to point configuration (high cap. cable with 6 dB attenuation) with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. I, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = -2.346371\%$ | $t_{max} = 2.853604\%$ | $t_{ava} = 0.453641\%$ |

|-------------------------|------------------------|------------------------|

|-------------------------|------------------------|------------------------|

## V30-11.64d

Input to output offset, point to point configuration (high cap. cable with 6 dB attenuation) with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. I, jitter 2015 Hz/0,05 UI

Conformance PASSED

| $t_{min} = -2.746381\%$ | $t_{max} = 2.853604\%$ | $t_{ava} = 0.853604\%$ |

|-------------------------|------------------------|------------------------|

|-------------------------|------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

## 9.5 Config. II: Binary ones, different jitter

#### V30-11.8a

Input to output offset, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. II, jitter 5 Hz / 0,5 UI

Conformance PASSED

| $t_{min} = 0.588020\%$ | $t_{max} = 8.588031\%$ | $t_{ava} = 6.588033\%$ |

|------------------------|------------------------|------------------------|

|------------------------|------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.8b

Input to output offset, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. II, jitter 20 Hz / 0,125 UI

Conformance PASSED

|--|

## V30-11.8c

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. II, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 0.788022\%$ | $t_{max} = 8.788033\%$ | $t_{ava} = 7.188031\%$ |

|------------------------|------------------------|------------------------|

|------------------------|------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.8d

Input to output offset, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. II, jitter 2015 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 0.588020\%$ $t_{max} = 8.588031\%$ $t_{ava} = 5.388024\%$ |

|----------------------------------------------------------------------|

|----------------------------------------------------------------------|

Measurement finished. Expected TAV-count reached.

## 9.6 Config. II: Octet 0x0AA, different jitter

#### V30-11.28a

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus, with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D- and D-Echo channels, restricted power at 32 V.

config. II, jitter 5 Hz/0,5 UI

Conformance PASSED

| $t_{min} = 0.788022\%$ | $t_{max} = 8.788033\%$ | $t_{ava} = 8.388015\%$ |

|------------------------|------------------------|------------------------|

|------------------------|------------------------|------------------------|

### V30-11.28b

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus, with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D- and D-Echo channels, restricted power at 32 V.

config. II, jitter 20 Hz / 0,125 UI

Conformance PASSED

| $t_{min} = 0.588020\%$ $t_{max} = 8.588031\%$ $t_{ava} = 5.788020\%$ | $t_{min} = 0.588020\%$ |  | $L_{ava} = 5.788020\%$ |

|----------------------------------------------------------------------|------------------------|--|------------------------|

|----------------------------------------------------------------------|------------------------|--|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.28c

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus, with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D- and D-Echo channels, restricted power at 32 V.

config. II, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 2.188024\%$ | $t_{max} = 8.588031\%$ | $t_{ava} = 7.388022\%$ |

|------------------------|------------------------|------------------------|

|------------------------|------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.28d

Input to output offset, short passive bus configuration (low cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus, with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D- and D-Echo channels, restricted power at 32 V.

config. II, jitter 2015 Hz/0,05 UI

Conformance PASSED

|  |  | $t_{min} = 2.388026\%$ | $t_{max} = 8.788033\%$ | $t_{ava} = 5.988023\%$ |

|--|--|------------------------|------------------------|------------------------|

|--|--|------------------------|------------------------|------------------------|

## 9.7 Config. II: Binary zeros, different jitter

### V30-11.48a

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus, with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. II, jitter 5 Hz / 0,5 UI

Conformance PASSED

|  | $t_{min} = 0.788022\%$ | $t_{max} = 8.788033\%$ | $t_{ava} = 5.988023\%$ |

|--|------------------------|------------------------|------------------------|

|--|------------------------|------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.48b

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus, with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. II, jitter 20 Hz/0,125 UI

Conformance PASSED

| $t_{min} = 0.588020\%$ | $t_{max} = 8.588031\%$ | $t_{ava} = 6.188014\%$ |

|------------------------|------------------------|------------------------|

|------------------------|------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.48c

Input to output offset, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus, with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. II, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 0.788022\%$ | $t_{max} = 8.788033\%$ | $t_{ava} = 7.988021\%$ |

|------------------------|------------------------|------------------------|

|------------------------|------------------------|------------------------|

## V30-11.48d

Input to output offset, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus, with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. II, jitter 2015 Hz/0,05 UI

Conformance PASSED

| $t_{min} = -0.611989\%$ | $t_{max} = 8.588031\%$ | $t_{ava} = 6.188014\%$ |

|-------------------------|------------------------|------------------------|

|-------------------------|------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

## 9.8 Config. II: 2<sup>19</sup> – 1 PRBS, different jitter

#### V30-11.68a

Input to output offset, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. II, jitter 5 Hz / 0,5 UI

Conformance PASSED

| $t_{min} = 0.788022\%$ | $t_{max} = 8.788033\%$ | $t_{ava} = 8.388015\%$ |

|------------------------|------------------------|------------------------|

|------------------------|------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.68b

Input to output offset, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. II, jitter 20 Hz/0,125 UI

Conformance PASSED

|--|

## V30-11.68c

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. II, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 0.588020\%$ | $t_{max} = 8.588031\%$ | $t_{ava} = 7.388022\%$ |

|------------------------|------------------------|------------------------|

|------------------------|------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.68d

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. II, jitter 2015 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 0.788022\%$ $t_{max} = 8.788033\%$ $t_{ava} = 7.988021\%$ |

|----------------------------------------------------------------------|

|----------------------------------------------------------------------|

Measurement finished. Expected TAV-count reached.

## 9.9 Config. IV: Binary ones, different jitter

#### V30-11.20a

Input to output offset, ideal configuration (direct connection TE to NT) with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IV, jitter 5 Hz / 0,5 UI

Conformance PASSED

| $t_{min} = 4.238429\%$ | $t_{max} = 11.038432\%$ | $t_{ava} = 9.038434\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

### V30-11.20b

Input to output offset, ideal configuration (direct connection TE to NT) with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IV, jitter 20 Hz / 0,125 UI

Conformance PASSED

| $t_{min} = 4.238429\%$ | $t_{max} = 11.038432\%$ | $t_{ava} = 9.038434\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.20c

Input to output offset, ideal configuration (direct connection TE to NT) with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IV, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 4.238429\%$ | $t_{max} = 11.838422\%$ | $t_{ava} = 8.238420\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.20d

Input to output offset, ideal configuration (direct connection TE to NT) with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IV, jitter 2015 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 4.238429\%$ $t_{max} = 11.438427\%$ $t_{ava} = 8.238420\%$ |  |

|-----------------------------------------------------------------------|--|

|-----------------------------------------------------------------------|--|

## 9.10 Config. IV: Octet 0x0AA, different jitter

## V30-11.40a

Input to output offset, ideal configuration (direct connection TE to NT) with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D- and D-Echo channels, restricted power at 32 V.

config. IV, jitter 5 Hz / 0,5 UI

Conformance PASSED

| $t_{min} = 3.438416\%$ | $t_{max} = 11.038432\%$ | $t_{ava} = 9.438429\%$ |

|------------------------|-------------------------|------------------------|

|                        |                         |                        |

Measurement finished. Expected TAV-count reached.

#### V30-11.40b

Input to output offset, ideal configuration (direct connection TE to NT) with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D- and D-Echo channels, restricted power at 32 V.

config. IV, jitter 20 Hz/0,125 UI

Conformance PASSED

| $t_{min} = 3.438416\%$ | $t_{max} = 11.038432\%$ | $t_{ava} = 9.038434\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.40c

Input to output offset, ideal configuration (direct connection TE to NT) with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D- and D-Echo channels, restricted power at 32 V.

config. IV, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 3.438416\%$ | $t_{max} = 11.038432\%$ | $t_{ava} = 10.238419\%$ |

|------------------------|-------------------------|-------------------------|

|------------------------|-------------------------|-------------------------|

## V30-11.40d

Input to output offset, ideal configuration (direct connection TE to NT) with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D- and D-Echo channels, restricted power at 32 V.

config. IV, jitter 2015 Hz / 0,05 UI

Conformance PASSED

Measurement finished. Expected TAV-count reached.

## 9.11 Config. IV: Binary zeros, different jitter

#### V30-11.60a

Input to output offset, ideal configuration (direct connection TE to NT) with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IV, jitter 5 Hz/0,5 UI

Conformance PASSED

| $t_{min} = 3.438416\%$ | $t_{max} = 11.038432\%$ | $t_{ava} = 9.438429\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.60b

Input to output offset, ideal configuration (direct connection TE to NT) with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IV, jitter 20 Hz/0,125 UI

Conformance PASSED

| $t_{min} = 4.238429\%$ $t_{max} = 11.038432\%$ | $t_{ava} = 9.438429\%$ |

|------------------------------------------------|------------------------|

|------------------------------------------------|------------------------|

## V30-11.60c

Input to output offset, ideal configuration (direct connection TE to NT) with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IV, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 3.438416\%$ | $t_{max} = 11.038432\%$ | $t_{ava} = 10.238419\%$ |

|------------------------|-------------------------|-------------------------|

|------------------------|-------------------------|-------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.60d

Input to output offset, ideal configuration (direct connection TE to NT) with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IV, jitter 2015 Hz/0,05 UI

Conformance PASSED

|--|

Measurement finished. Expected TAV-count reached.

## 9.12 Config. IV: 2<sup>19</sup> – 1 PRBS, different jitter

#### V30-11.80a

Input to output offset, ideal configuration (direct connection TE to NT) with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IV, jitter 5 Hz / 0,5 UI

Conformance PASSED

| $t_{min} = 3.438416\%$ | $t_{max} = 11.038432\%$ | $t_{ava} = 8.238420\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

## V30-11.80b

Input to output offset, ideal configuration (direct connection TE to NT) with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IV, jitter 20 Hz/0,125 UI

Conformance PASSED

| $t_{min} = 4.238429\%$ | $t_{max} = 11.038432\%$ | $t_{ava} = 9.838424\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.80c

Input to output offset, ideal configuration (direct connection TE to NT) with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IV, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 3.438416\%$ | $t_{max} = 11.038432\%$ | $t_{ava} = 7.838426\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.80d

Input to output offset, ideal configuration (direct connection TE to NT) with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IV, jitter 2015 Hz / 0,05 UI

Conformance PASSED

| $t_{min} = 3.038421\%$ $t_{max} = 11.038432\%$ $t_{ava} = 9.038434\%$ |  |

|-----------------------------------------------------------------------|--|

|-----------------------------------------------------------------------|--|

## 9.13 Config. IIIa: Binary ones, different jitter

## V30-11.12a

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIa, jitter 5 Hz/0,5 UI

Conformance PASSED

|  | $t_{min} = 8.638420\%$ | $t_{max} = 11.838422\%$ | $t_{ava} = 10.638413\%$ |

|--|------------------------|-------------------------|-------------------------|

|--|------------------------|-------------------------|-------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.12b

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIa, jitter 20 Hz/0,125 UI

Conformance PASSED

| $t_{min} = 8.238425\%$ | $t_{max} = 11.838422\%$ | $t_{ava} = 9.438429\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.12c

Input to output offset, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIa, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 8.238425\%$ | $t_{max} = 11.838422\%$ | $t_{ava} = 10.638413\%$ |

|------------------------|-------------------------|-------------------------|

|------------------------|-------------------------|-------------------------|

## V30-11.12d

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIa, jitter 2015 Hz/0,05 UI

Conformance PASSED

| $l_{min} = 5.65645476$ $l_{max} = 11.65642276$ $l_{ava} = 10.25641976$ |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

Measurement finished. Expected TAV-count reached.

## 9.14 Config. IIIa: Octet 0x0AA, different jitter

#### V30-11.32a

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D-and D-Echo channels, restricted power at 32 V.

config. IIIa, jitter 5 Hz / 0,5 UI

Conformance PASSED

| $t_{min} = 7.838430\%$ | $t_{max} = 11.038432\%$ | $t_{ava} = 10.238419\%$ |

|------------------------|-------------------------|-------------------------|

|------------------------|-------------------------|-------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.32b

Input to output offset, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D-and D-Echo channels, restricted power at 32 V.

config. IIIa, jitter 20 Hz / 0,125 UI

Conformance PASSED

| $t_{min} = 8.238425\%$ $t_{max} = 11.838422\%$ $t_{ava} = 9.038434\%$ | $t_{max} = 11.838422\%$ $t_{ava} = 9.038434\%$ |

|-----------------------------------------------------------------------|------------------------------------------------|

|-----------------------------------------------------------------------|------------------------------------------------|

## V30-11.32c

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D-and D-Echo channels, restricted power at 32 V.

config. IIIa, jitter 50 Hz / 0,05 UI

Conformance PASSED

| $t_{min} = 8.238425\%$ $t_{max} = 11.838422\%$ $t_{ava} = 9.438429$ | 6 |

|---------------------------------------------------------------------|---|

|---------------------------------------------------------------------|---|

Measurement finished. Expected TAV-count reached.

#### V30-11.32d

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D-and D-Echo channels, restricted power at 32 V.

config. IIIa, jitter 2015 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 2.238431\%$ $t_{max} = 11.838422\%$ $t_{ava} = 9.038434\%$ | $t_{min} = 2.238431\%$ |

|-----------------------------------------------------------------------|------------------------|

|-----------------------------------------------------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

## 9.15 Config. IIIa: Binary zeros, different jitter

#### V30-11.52a

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIa, jitter 5 Hz / 0,5 UI

Conformance PASSED

## V30-11.52b

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIa, jitter 20 Hz / 0,125 UI

Conformance PASSED

| $t_{min} = 8.238425\%$ $t_{max} = 11.838422\%$ $t_{ava} = 11.438427\%$ |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

Measurement finished. Expected TAV-count reached.

### V30-11.52c

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIa, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 8.238425\%$ | $t_{max} = 11.838422\%$ | $t_{ava} = 8.638415\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.52d

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIa, jitter 2015 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 2.238431\%$ | $t_{max} = 11.838422\%$ | $t_{ava} = 9.438429\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

## 9.16 Config. IIIa: 2<sup>19</sup> – 1 PRBS, different jitter

## V30-11.72a

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, with the UUT-TE adjacent to the signal source, with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIa, jitter 5 Hz / 0,5 UI

Conformance PASSED

| $t_{min} = 8.638420\%$ | $t_{max} = 11.838422\%$ | $t_{ava} = 10.638413\%$ |

|------------------------|-------------------------|-------------------------|

|                        |                         |                         |

Measurement finished. Expected TAV-count reached.

#### V30-11.72b

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, with the UUT-TE adjacent to the signal source, with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIa, jitter 20 Hz/0,125 UI

Conformance PASSED

| $t_{min} = 8.238425\%$ | $t_{max} = 11.838422\%$ | $t_{ava} = 8.638415\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.72c

Input to output offset, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 7 TEs clustered at the far end of the bus, with the UUT-TE adjacent to the signal source, with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIa, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 8.238425\%$ | $t_{max} = 11.838422\%$ | $t_{ava} = 10.238419\%$ |

|------------------------|-------------------------|-------------------------|

|                        |                         |                         |

## V30-11.72d

Input to output offset, short passive bus configuration (high cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, with the UUT-TE adjacent to the signal source, with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIa, jitter 2015 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 6.638422\%$ $t_{max} = 11.838422\%$ $t_{ava} = 10.238419\%$ |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

Measurement finished. Expected TAV-count reached.

#### 9.17 Config. IIIb: Binary ones, different jitter

#### V30-11.16a

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIb, jitter 5 Hz/0,5 UI

Conformance PASSED

| $t_{min} = 8.638420\%$ | $t_{max} = 11.438427\%$ | $t_{ava} = 8.638415\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.16b

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIb, jitter 20 Hz/0,125 UI

Conformance PASSED

| $t_{min} = 8.238425\%$ $t_{max} = 11.438427\%$ $t_{ava} = 10.238419\%$ |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

## V30-11.16c

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIb, jitter 50 Hz / 0,05 UI

Conformance PASSED

| $t_{min} = 7.838430\%$ $t_{max} = 11.438427\%$ $t_{ava} = 9.038434\%$ |

|-----------------------------------------------------------------------|

|-----------------------------------------------------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.16d

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with all binary ones in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIb, jitter 2015 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 2.238431\%$ $t_{max} = 11.838422\%$ $t_{ava} = 9.838424\%$ | $t_{min} = 2.238431\%$ $t_{max} = 11.838422\%$ $t_{ava} =$ | 38474% |

|-----------------------------------------------------------------------|------------------------------------------------------------|--------|

|-----------------------------------------------------------------------|------------------------------------------------------------|--------|

Measurement finished. Expected TAV-count reached.

## 9.18 Config. IIIb: Octet 0x0AA, different jitter

#### V30-11.36a

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D-and D-Echo channels, restricted power at 32 V.

config. IIIb, jitter 5 Hz / 0,5 UI

Conformance PASSED

| $t_{min} = 7.838430\%$ $t_{max} = 11.438427\%$ $t_{ava} = 7.838426\%$ | 160/- |

|-----------------------------------------------------------------------|-------|

|-----------------------------------------------------------------------|-------|

## V30-11.36b

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D-and D-Echo channels, restricted power at 32 V.

config. IIIb, jitter 20 Hz/0,125 UI

Conformance PASSED

| $t_{min} = 7.838430\% \qquad t_{max} = 11.438427\% \qquad t_{ava} = 9.838424\%$ |  |

|---------------------------------------------------------------------------------|--|

|---------------------------------------------------------------------------------|--|

Measurement finished. Expected TAV-count reached.

#### V30-11.36c

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D-and D-Echo channels, restricted power at 32 V.

config. IIIb, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 7.838430\%$ | $t_{max} = 11.438427\%$ | $t_{ava} = 9.838424\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.36d

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with the octet 0x0AA in both B-channels and binary ones in the D-and D-Echo channels, restricted power at 32 V.

config. IIIb, jitter 2015 Hz / 0,05 UI

Conformance PASSED

| $t_{min} = 6.638422\%$ | $t_{max} = 11.838422\%$ | $t_{ava} = 7.438431\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

## 9.19 Config. IIIb: Binary zeros, different jitter

#### V30-11.56a

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu s$  delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIb, jitter 5 Hz/0,5 UI

Conformance PASSED

|  | $t_{min} = 8.238425\%$ | $t_{max} = 11.438427\%$ | $t_{ava} = 8.638415\%$ |

|--|------------------------|-------------------------|------------------------|

|--|------------------------|-------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.56b

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIb, jitter 20 Hz/0,125 UI

Conformance PASSED

| $t_{min} = 7.838430\%$ | $t_{max} = 11.438427\%$ | $t_{ava} = 9.038434\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.56c

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIb, jitter 50 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 7.838430\%$ | $t_{max} = 11.438427\%$ | $t_{ava} = 10.238419\%$ |

|------------------------|-------------------------|-------------------------|

|------------------------|-------------------------|-------------------------|

## V30-11.56d

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with an input sequence of continuous frames with all binary zeroes in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIb, jitter 2015 Hz / 0,05 UI

Conformance PASSED

|  | $t_{min} = 6.638422\%$ | $t_{max} = 11.838422\%$ | $t_{ava} = 9.038434\%$ |

|--|------------------------|-------------------------|------------------------|

|--|------------------------|-------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

# 9.20 Config. IIIb: 2<sup>19</sup> – 1 PRBS, different jitter

#### V30-11.76a

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, with the UUT-TE adjacent to the signal source, with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIb, jitter 5 Hz/0,5 UI

Conformance PASSED

| $t_{min} = 8.638420\%$ | $t_{max} = 11.438427\%$ | $t_{ava} = 9.838424\%$ |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.76b

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, with the UUT-TE adjacent to the signal source, with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIb, jitter 20 Hz/0,125 UI

Conformance PASSED

| $t_{min} = 7.838430\%$ $t_{max} = 11.438427\%$ | $t_{ava} = 11.038432\%$ |

|------------------------------------------------|-------------------------|

|------------------------------------------------|-------------------------|

## V30-11.76c

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, with the UUT-TE adjacent to the signal source, with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIb, jitter 50 Hz / 0,05 UI

Conformance PASSED

| $t_{min} = 7.838430\%$ $t_{max} = 11.438427\%$ $t_{ava} = 9.838424\%$ |

|-----------------------------------------------------------------------|

|-----------------------------------------------------------------------|

Measurement finished. Expected TAV-count reached.

#### V30-11.76d

Input to output offset, short passive bus configuration (low cap. cable with  $2\mu$ s delay) with 7 TEs clustered at the far end of the bus, with the UUT-TE adjacent to the signal source, with an input sequence of continuous frames with a  $2^{19} - 1$  PRBS in D-, D-Echo and both B-channels, restricted power at 32 V.

config. IIIb, jitter 2015 Hz/0,05 UI

Conformance PASSED

| $t_{min} = 2.238431\%$ $t_{max} = 11.838422\%$ $t_{ava} = 9.438429\%$ |

|-----------------------------------------------------------------------|

|-----------------------------------------------------------------------|

# **10** Receiver sensitivity

## 10.1 config. IIIa: 1.5 dB attenuated, different jitter

#### V30-17.20a

Receiver sensitivity with jitter, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. IIIa, jitter 5 Hz/0,5 UI

Conformance PASSED

| Intervals = 1           | Bit Error Count $= 0.000000$ |

|-------------------------|------------------------------|

| Errored Intervals $= 0$ | Bit Error Rate $= 0.000000$  |

| Time = $60.000000$ s    |                              |

## V30-17.20b

Receiver sensitivity with jitter, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. IIIa, jitter 20 Hz / 0,125 UI

Conformance PASSED

## V30-17.20c

Receiver sensitivity with jitter, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. IIIa, jitter 50 Hz / 0,05 UI

Conformance PASSED

## V30-17.20d

Receiver sensitivity with jitter, short passive bus configuration (high cap. cable with  $2 \mu$ s delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. IIIa, jitter 2015 Hz/0,05 UI

## 10.2 config. IIIa: 1.5 dB gain, different jitter

### V30-17.24a

Receiver sensitivity with jitter, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with a 1.5 dB gain signal source, restricted power at 32 V.

config. IIIa, jitter 5 Hz / 0,5 UI

Conformance PASSED

#### V30-17.24b

Receiver sensitivity with jitter, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with a 1.5 dB gain signal source, restricted power at 32 V.

config. IIIa, jitter 20 Hz/0,125 UI

Conformance PASSED

#### V30-17.24c

Receiver sensitivity with jitter, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with a 1.5 dB gain signal source, restricted power at 32 V.

config. IIIa, jitter 50 Hz/0,05 UI

Conformance PASSED

#### V30-17.24d

Receiver sensitivity with jitter, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with a 1.5 dB gain signal source, restricted power at 32 V.

config. IIIa, jitter 2015 Hz/0,05 UI

## 10.3 config. IIIb: 1.5 dB attenuated, different jitter

#### V30-17.28a

Receiver sensitivity with jitter, short passive bus configuration (low cap. cable with  $2 \mu s$  delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. IIIb, jitter 5 Hz / 0,5 UI

Conformance PASSED

#### V30-17.28b

Receiver sensitivity with jitter, short passive bus configuration (low cap. cable with  $2 \mu s$  delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. IIIb, jitter 20 Hz/0,125 UI

Conformance PASSED

#### V30-17.28c

Receiver sensitivity with jitter, short passive bus configuration (low cap. cable with  $2 \mu s$  delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. IIIb, jitter 50 Hz/0,05 UI

Conformance PASSED

#### V30-17.28d

Receiver sensitivity with jitter, short passive bus configuration (low cap. cable with  $2 \mu s$  delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. IIIb, jitter 2015 Hz / 0,05 UI

## 10.4 config. IIIb: 1.5 dB gain, different jitter

### V30-17.32a

Receiver sensitivity with jitter, short passive bus configuration (low cap. cable with  $2 \mu s$  delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with a 1.5 dB gain signal source, restricted power at 32 V.

config. IIIb, jitter 5 Hz/0,5 UI

Conformance PASSED

#### V30-17.32b

Receiver sensitivity with jitter, short passive bus configuration (low cap. cable with  $2 \mu s$  delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with a 1.5 dB gain signal source, restricted power at 32 V.

config. IIIb, jitter 20 Hz/0,125 UI

Conformance PASSED

#### V30-17.32c

Receiver sensitivity with jitter, short passive bus configuration (low cap. cable with  $2 \mu s$  delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with a 1.5 dB gain signal source, restricted power at 32 V.

config. IIIb, jitter 50 Hz/0,05 UI

Conformance PASSED

#### V30-17.32d

Receiver sensitivity with jitter, short passive bus configuration (low cap. cable with  $2 \mu s$  delay) with 7 TEs clustered at the far end of the bus, and the UUT-TE adjacent to the signal source with a 1.5 dB gain signal source, restricted power at 32 V.

config. IIIb, jitter 2015 Hz/0,05 UI

## 10.5 config. I: 1.5 dB attenuated, 200 kHz noise, different jitter

## V30-17.4a

Receiver sensitivity with 200 kHz sine wave noise and jitter, short point to point configuration (high cap. cable with 6 dB attenuation) with a with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. I, jitter 5 Hz/0,5 UI

Conformance PASSED

## V30-17.4b

Receiver sensitivity with 200 kHz sine wave noise and jitter, short point to point configuration (high cap. cable with 6 dB attenuation) with a with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. I, jitter 20 Hz / 0,125 UI

Conformance PASSED

## V30-17.4c

Receiver sensitivity with 200 kHz sine wave noise and jitter, short point to point configuration (high cap. cable with 6 dB attenuation) with a with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. I, jitter 50 Hz/0,05 UI

Conformance PASSED

## V30-17.4d

Receiver sensitivity with 200 kHz sine wave noise and jitter, short point to point configuration (high cap. cable with 6 dB attenuation) with a with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. I, jitter 2015 Hz/0,05 UI

## 10.6 config. I: 1.5 dB attenuated, 2 MHz noise, different jitter

### V30-17.8a

Receiver sensitivity with 2 MHz sine wave noise and jitter, short point to point configuration (high cap. cable with 6 dB attenuation) with a with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. I, jitter 5 Hz/0,5 UI

Conformance PASSED

#### V30-17.8b

Receiver sensitivity with 2 MHz sine wave noise and jitter, short point to point configuration (high cap. cable with 6 dB attenuation) with a with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. I, jitter 20 Hz/0,125 UI

Conformance PASSED

#### V30-17.8c

Receiver sensitivity with 2 MHz sine wave noise and jitter, short point to point configuration (high cap. cable with 6 dB attenuation) with a with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. I, jitter 50 Hz/0,05 UI

Conformance PASSED

#### V30-17.8d

Receiver sensitivity with 2 MHz sine wave noise and jitter, short point to point configuration (high cap. cable with 6 dB attenuation) with a with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. I, jitter 2015 Hz/0,05 UI

## 10.7 config. II: 1.5 dB attenuated, different jitter

## V30-17.12a

Receiver sensitivity with jitter, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. II, jitter 5 Hz/0,5 UI

Conformance PASSED

## V30-17.12b

Receiver sensitivity with jitter, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. II, jitter 20 Hz/0,125 UI

Conformance PASSED

#### V30-17.12c

Receiver sensitivity with jitter, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. II, jitter 50 Hz / 0,05 UI

Conformance PASSED

## V30-17.12d

Receiver sensitivity with jitter, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with a 1.5 dB attenuated signal source, restricted power at 32 V.

config. II, jitter 2015 Hz / 0,05 UI

## 10.8 config. II: 1.5 dB gain, different jitter

### V30-17.16a

Receiver sensitivity with jitter, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with a 1.5 dB gain signal source, restricted power at 32 V.

config. II, jitter 5 Hz/0,5 UI

Conformance PASSED

#### V30-17.16b

Receiver sensitivity with jitter, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with a 1.5 dB gain signal source, restricted power at 32 V.

config. II, jitter 20 Hz/0,125 UI

Conformance PASSED

#### V30-17.16c

Receiver sensitivity with jitter, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with a 1.5 dB gain signal source, restricted power at 32 V.

config. II, jitter 50 Hz/0,05 UI

Conformance PASSED

#### V30-17.16d

Receiver sensitivity with jitter, short passive bus configuration (high cap. cable with  $2 \mu s$  delay) with 8 TEs (including the UUT-TE) clustered at the far end of the bus with a 1.5 dB gain signal source, restricted power at 32 V.

config. II, jitter 2015 Hz / 0,05 UI

## 10.9 config. IV: 1.5 dB gain, different jitter

#### V30-17.36a

Receiver sensitivity with jitter, ideal configuration (direct connection UUT-TE to NT) with a 1.5 dB gain signal source, restricted power at 32 V.

config. IV, jitter 5 Hz / 0,5 UI

Conformance PASSED

#### V30-17.36b

Receiver sensitivity with jitter, ideal configuration (direct connection UUT-TE to NT) with a 1.5 dB gain signal source, restricted power at 32 V.

config. IV, jitter 20 Hz / 0,125 UI